Table 17-5: word length selection -6 – Cirrus Logic EP73xx User Manual

Page 152

17-6

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

UART and SIR Encoder

17

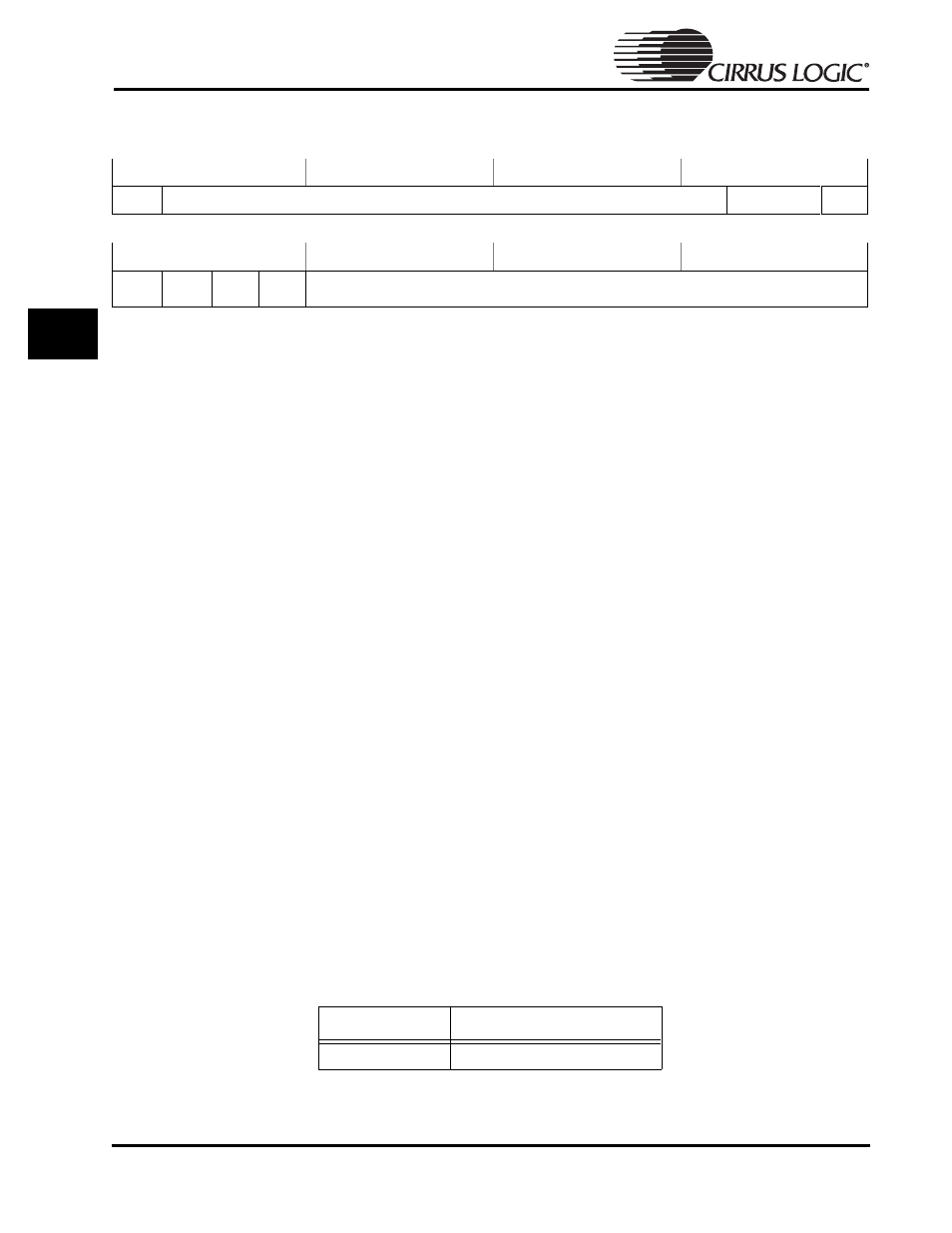

Bit Rate and Line Control Registers (UBRLCR1 and UBRLCR2)

Address:

0x8000.04C0 and 0x8000.14C0, Read / Write

Bit Descriptions:

Bit rate divisor:This 12-bit field sets the bit rate. If the system is operating from

PLL clock, then the bit rate divider is fed by a clock frequency of

3.6864 MHz. This is the Bus clock (PLL/4) divided by 10. This is

further divided internally by 16 to give the bit rate. The formula to

give the divisor value when running in PLL mode is:

Divisor Value = 230400/(bit rate divisor + 1)

A value of zero in this field is illegal when running from the PLL

clock. The clock frequency fed to the UARTs when in 13 MHz

mode is 1.975 MHz. In this mode, zero is a legal divisor for the

maximum baud rate. See

for some

examples of the divisor values for the various bit rates and clock

sources.

BREAK:

Setting this bit will drive the TX output active (high) to generate a

break.

PRTEN:

Parity enable bit. Setting this bit enables the parity detection and

generation

EVENPRT: Even parity bit. Setting this bit sets parity generation and checking

to even parity. Clearing set odd parity. This bit has not affect if

PRTEN is cleared

XSTOP:

Extra stop bit. Setting this bit will cause the UART to transmit two

stop bits after each data byte. Clearing this bit will transmit one

stop bit after each data byte.

FIFOEN:

Set to enable FIFO of Rx and Tx data. Clear will disable FIFO (i.e.,

set depth to one byte)

WRDLEN: This two bit field selects the word length according to the table

below:

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

WRDLEN

FIFOEN

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

XSTOP

EVENPR

T

PRTEN

BREAK

Bit Rate Divisor

Table 17-5: Word Length Selection

WRDLEN

Word Length

00

5 bits