Arm720t core coprocessor registers, Arm720t core coprocessor registers -8, Figure 2-3. register organization summary -8 – Cirrus Logic EP73xx User Manual

Page 34

2-8

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

CPU Core

2

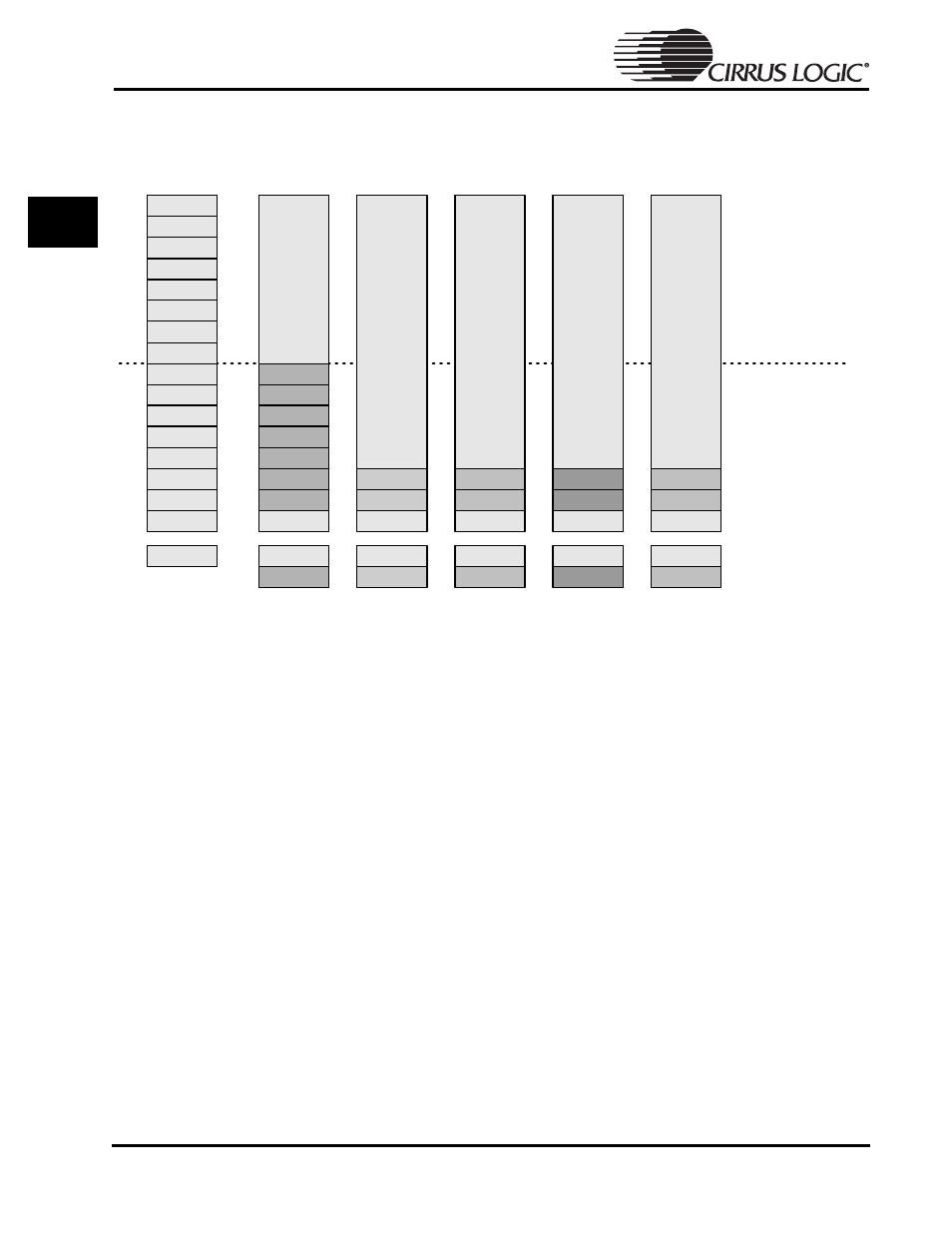

User mode in Thumb state generally limits access to r0-r7. There are a few

instructions that allow access to the high registers. For the 5 exceptions, the processor

must revert to ARM state.

R0-R12:

General purpose read/write 32-bit registers

R13 (sp):

Stack Pointer

R14 (lr):

Link Register

R15 (pc):

Program Counter

CPSR:

Current Program Status Register (contains condition codes and

operating modes)

SPSR:

Saved Program Status Register (saves CPSR when exception occurs)

ARM720T Core Coprocessor Registers

The ARM720T core has 16 coprocessor registers for control over the MMU. See

Updates to the co-processor registers are written using the CP15

instruction.

Figure 2-3. Register Organization Summary

r0

r6

r5

r4

r3

r2

r1

c p sr

r1 5 (p c)

r1 4 (lr)

r1 3 (sp )

r1 2

r1 1

r1 0

r9

r1 4 (lr)

r1 3 (sp )

r1 2

r1 1

r1 0

r9

sp sr

B a n k e d

B a n k e d

r8

r7

r8

U se r

F IQ

IR Q

SV C

U n d e f

A bo r t

T h u m b sta te

L ow re g iste rs

r1 4 (lr)

r1 3 (sp )

sp sr

B a n k ed

r1 4 (lr)

r1 3 (sp )

sp sr

B a n k e d

r1 4 (lr)

r1 3 (sp )

sp sr

B a n k e d

r1 4 (lr)

r1 3 (sp )

sp sr

T h u m b sta te

H ig h re g iste rs