Cirrus Logic EP73xx User Manual

Page 65

EP7309/11/12 User’s Manual - DS508UM4

5-5

Copyright Cirrus Logic, Inc. 2003

System Registers

55

5

TC1M:

Timer counter 1 mode. Setting this bit sets TC1 clock to prescale

mode, clearing it sets free running mode.

TC1S:

Timer counter 1 clock source. Setting this bit sets the TC1 clock

source to 512 kHz, clearing it sets the clock source to 2 kHz.

Note: Refer to

“Operational Overview” on page 3-2

for more information on timers

when the PLL is set to 90 MHz.

TC2M:

Timer counter 2 mode. Setting this bit sets TC2 clock to prescale

mode, clearing it sets free running mode.

TC2S:

Timer counter 2 clock source. Setting this bit sets the TC2 clock

source to 512 kHz, clearing it sets the clock source to 2 kHz.

Note: Refer to

“Operational Overview” on page 3-2

for more information on timers

when the PLL is set to 90 MHz.

UART1EN: Internal UART enable bit. Setting this bit enables the internal

UART.

BZTOG:

Bit to drive (i.e. toggle) the buzzer output directly when software

mode of operation is selected (i.e. bit BZMOD=0).

BZMOD:

Buzzer drive mode select. When set, the buzzer source is

determined by BUZFREQ. When cleared, the

BUZ

output reflects

the state of the BZTOG bit.

DBGEN:

Forces the internal memory accesses (SRAM, boot ROM, register

space) to appear on the external address/data bus. Also outputs

the status of the internal IRQ and FIQ outputs of the interrupt

controller and the internal bus clock on bits of Port E.

LCDEN:

Enables the LCD controller when set.

CDENTX: CODEC interface TX enable bit. Setting this bit enables the

CODEC interface for data transmission to an external CODEC

device.

CDENRX: CODEC interface RX enable bit. Setting this bit enables the

CODEC interface for data reception from an external CODEC

device. Note that CDENRX and CDENTX must be enabled in

tandem, otherwise data may be lost.

SIREN:

SIR protocol encoding bit. This enables the IrDA input and output

from UART1 as opposed to logic level serial.

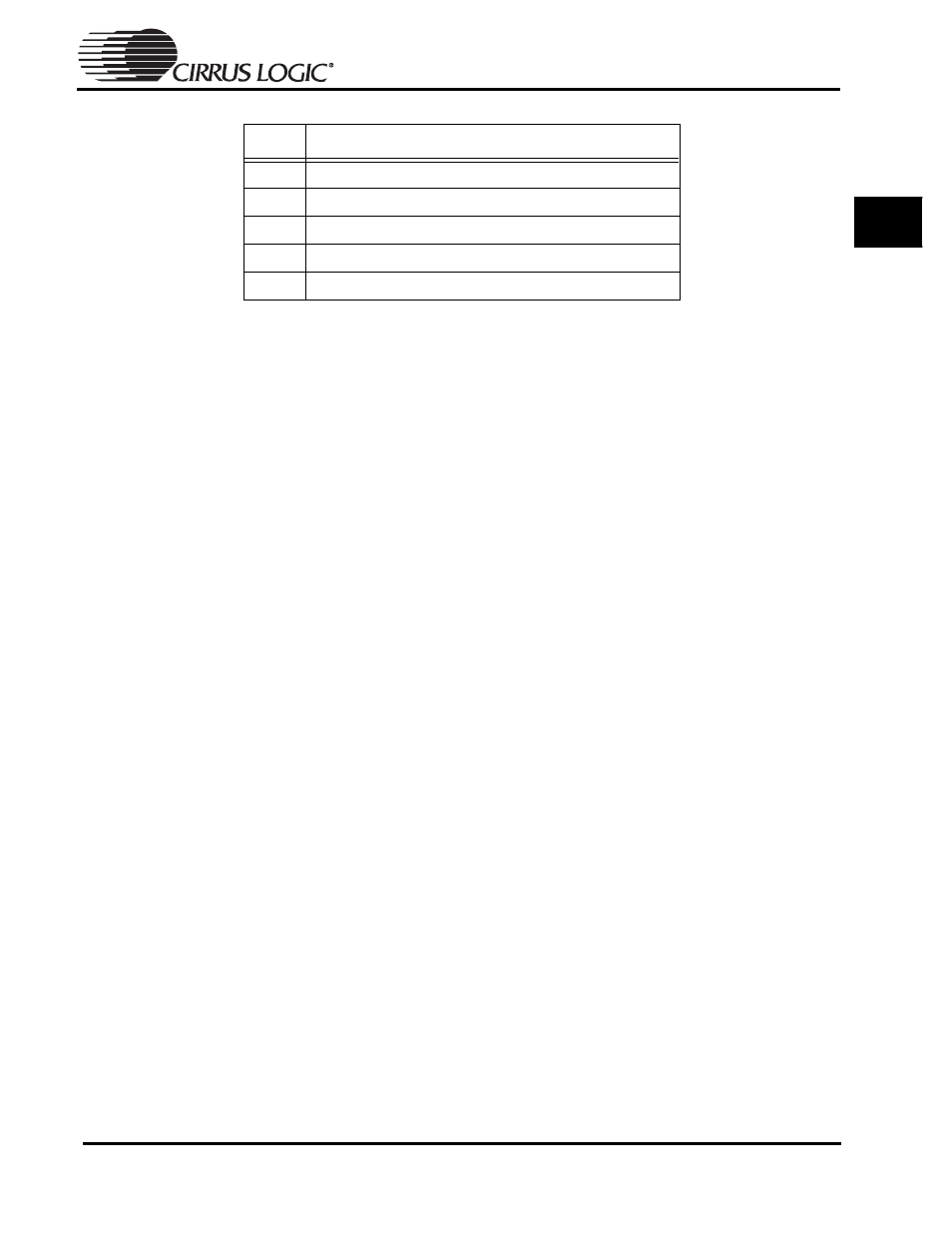

11

Column 3 high, all others Hi-Z

12

Column 4 high, all others Hi-Z

13

Column 5 high, all others Hi-Z

14

Column 6 high, all others Hi-Z

15

Column 7 high, all others Hi-Z

Table 5-2: Keyboard Column Drive State (Continued)

Value

Column Drive State