Enter the idle state register (halt), Power up sequence, Enter the idle state register (halt) -14 – Cirrus Logic EP73xx User Manual

Page 40: Power up sequence -14

2-14

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

CPU Core

2

The following register will allow the system software to put the processor into Idle

state.

Enter the Idle State Register (HALT)

Address:

0x8000.0800, Write Only

Definition:

A write to this location will put the system into the Idle State by

halting the clock to the processor until an interrupt is generated. A

write to this location while there is an active interrupt will have no

effect

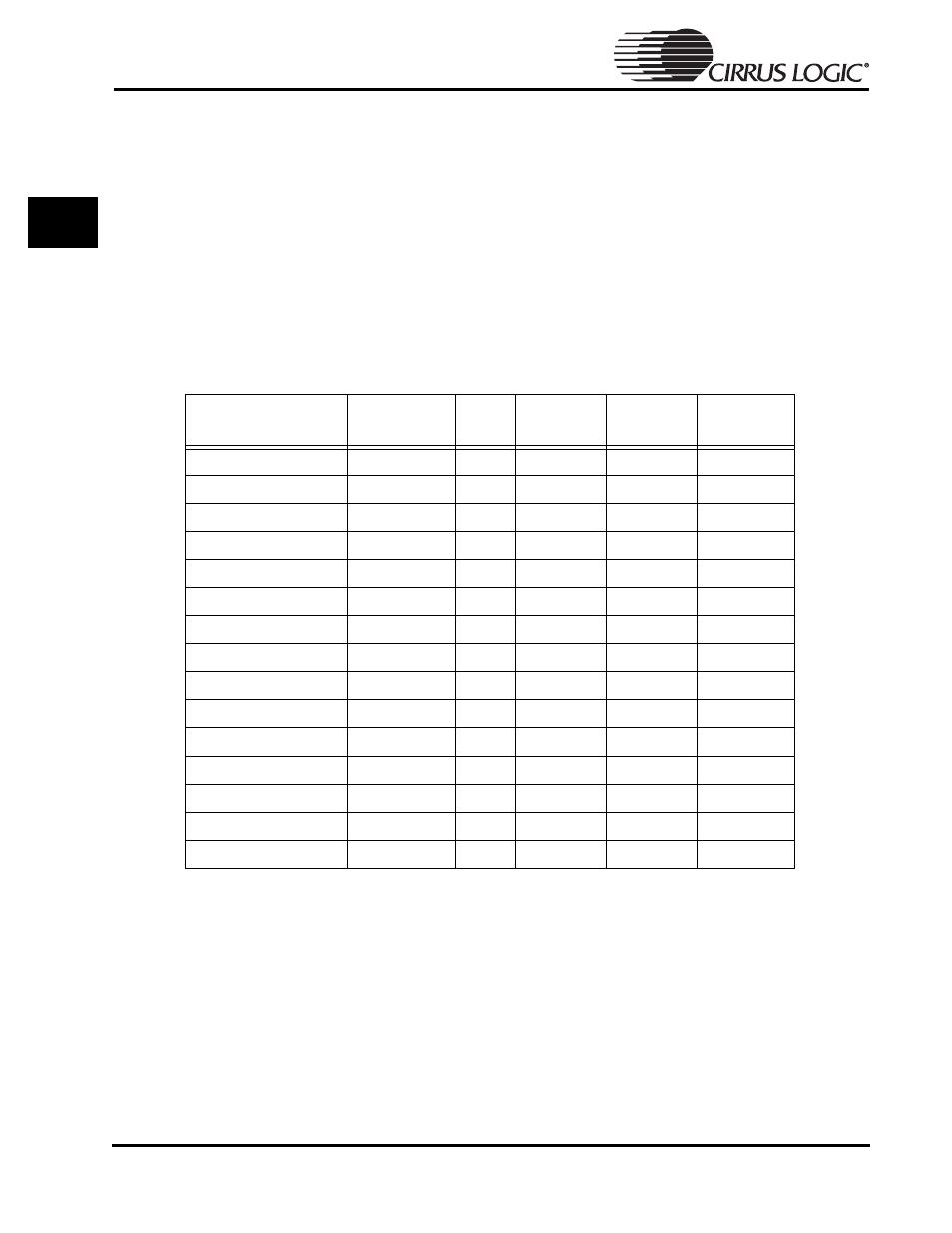

Below is a list of peripherals and clocks and their status during each of the three

states:

Power Up Sequence

The EP73xx has a power-up sequence that must be followed for a proper start. If any

of the recommended timing sequences below are violated, the part may not start

properly and may not recover without a hard reset.

1. Upon power-up,

nPOR

must be held low for a minimum of 100

µs after

Vdd has settled

Note: nURESET must be stable before nPOR rising.

Table 2-3: Status of Peripherals and Clocks by Operating State

Address (W/B)

Operating

Idle

Standby

nPOR

RESET

nURESET

RESET

SDRAM Control

On

On

SELFREF

Off

N/A

UARTs

On

On

Off

Reset

Reset

LCD FIFO

On

On

Reset

Reset

Reset

LCD

On

On

Off

Reset

Reset

ADC Interface

On

On

Off

Reset

Reset

SSI2 Interface

On

On

Off

Reset

Reset

DAI Interface

On

On

Off

Reset

Reset

CODEC

On

On

Off

Reset

Reset

Timers

On

On

Off

Reset

Reset

RTC

On

On

On

On

On

LED Flasher

On

On

On

Reset

Reset

DC-to-DC

On

On

Off

Reset

Reset

CPU

On

Off

Off

Reset

Reset

Interrupt Control

On

On

On

Reset

Reset

PLL/CLKEN Signal

On

On

Off

Off

Off