Standby state, Table 4-7: external interrupt sources -7 – Cirrus Logic EP73xx User Manual

Page 53

EP7309/11/12 User’s Manual - DS508UM4

4-7

Copyright Cirrus Logic, Inc. 2003

Interrupt Controller

44

4

Standby State

The Standby State equates to the system being switched “off” (i.e., no display, and the

main oscillator is shut down). If the 18.432–73.72 MHz mode is selected, the PLL will

be shut down. In the 13 MHz mode, if the CLKENSL bit is set low, the

CLKEN

signal

will be forced low and can, if required, be used to disable an external oscillator.

In Standby State, all system memory and state is maintained and system time is kept

current. The PLL/on-chip oscillator or external oscillator is disabled and the system is

static, except for the low-power watch crystal (32 kHz) oscillator and divider chain to

the RTC and LED flasher. The

RUN

signal is driven low, and can be used externally in

the system to power down other system modules.

When the EP73xx is in Standby State, external address and data buses are driven low.

The

RUN

signal is used internally to force these buses to be driven low. This is done to

prevent peripherals that are power-down from draining current.

In Standby State, internal peripherals’ signals are set to their Reset States.

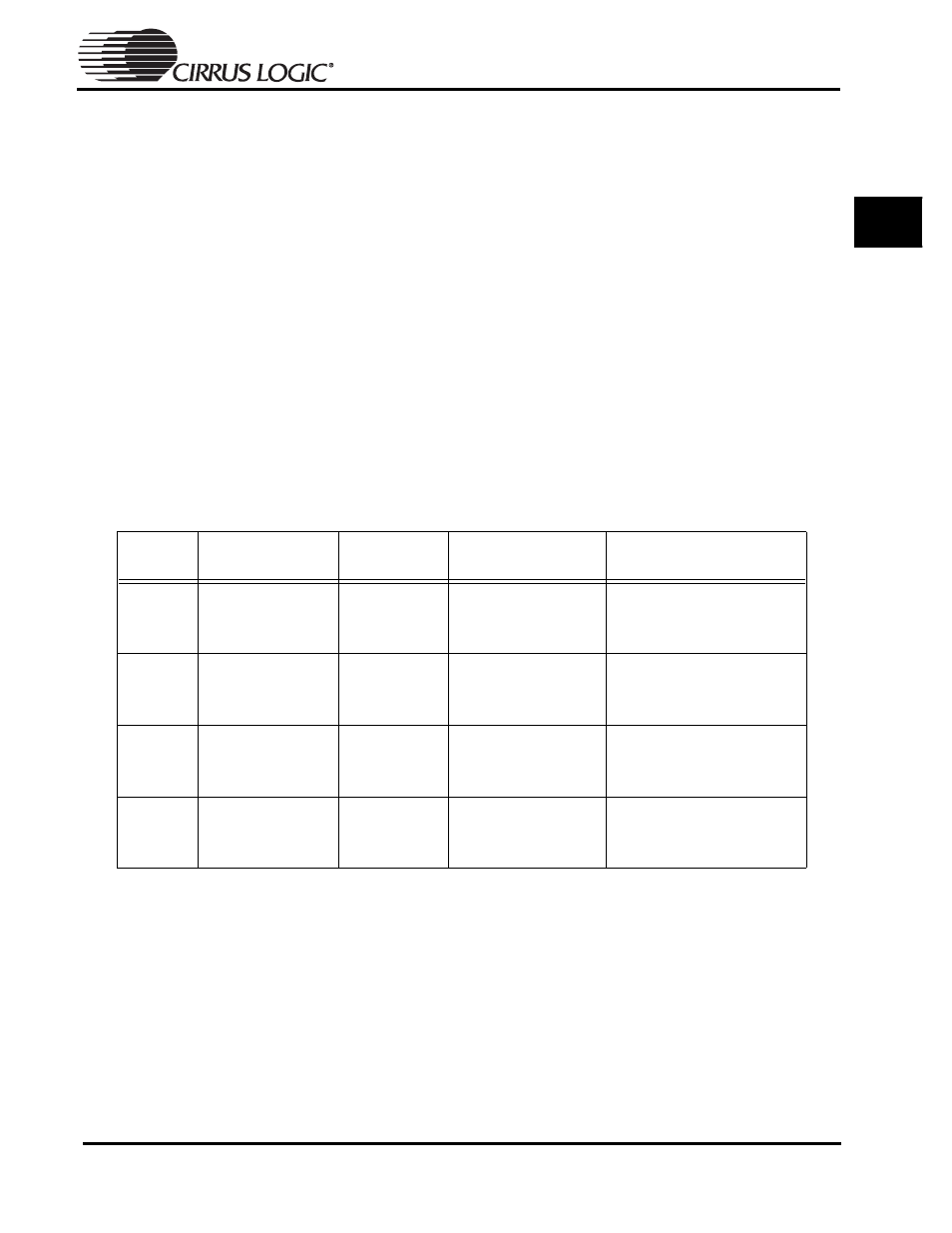

summarizes the five external interrupt sources and the effect they have on

the processor interrupts.

Table 4-7: External Interrupt Sources

Interrupt

Pin

Input State

Operating

State Latency

Idle State Latency

Standby State Latency

nEXTFIQ

Not deglitched; must be

active for 20

µs to be

detected

Worst-case

latency of 20

µs

Worst-case 20

µs: if only

single cycle instructions,

less than 1

µs

Including PLL / osc. settling time,

approx. 0.25 sec, or approx. 500

µs when in Idle State if in 13 MHz

mode with CLKENSL set

nEINT1–2

Not deglitched

Worst-case

latency of 20

µs

Worst-case 20

µs: if only

single cycle instructions,

less than 1

µs

Including PLL / osc. settling time,

approx. 0.25 sec, or approx. 500

µs when in Idle State if in 13 MHz

mode with CLKENSL set.

EINT3

Not deglitched

Worst-case

latency of 19.3

µs

Worst-case 20

µs: if only

single cycle instructions,

less than 1

µs

Including PLL / osc. settling time,

approx. 0.25 sec, or approx. 500

µs when in Idle State if in 13 MHz

mode with CLKENSL set.

nMEDCHG

Deglitched by

16.384 kHz clock; must

be active for at least

122

µs to be detected

Worst-case

latency of 141

µs

Worst-case latency

141

µs; if any single cycle

instructions = 125

µs

As above (note difference if in

13 MHz mode with CLKENSL set)