Ssi port register descriptions, Register configuration for extended mode, Ssi port register descriptions -4 – Cirrus Logic EP73xx User Manual

Page 122: Address, Bit descriptions, Smpclk

15-4

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

SSI Port

15

SSI Port Register Descriptions

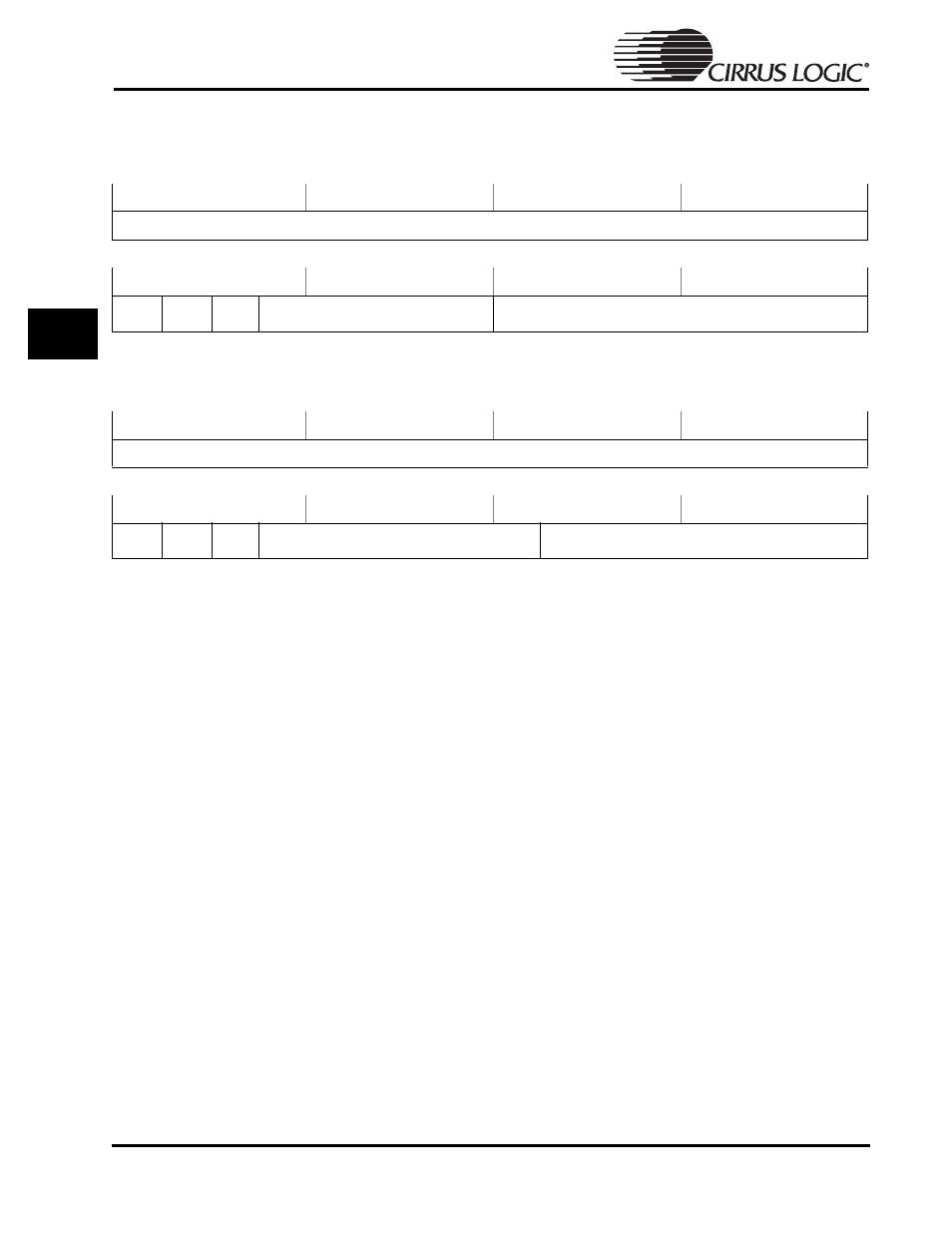

Synchronous Serial ADC Interface Data Register (SYNCIO)

Address:

0x8000.0500, Read / Write

Register Configuration for Extended Mode

Bit Descriptions:

ADC Configuration Length/Byte:When the ADCCON control bit in the

SYSCON3 register = 0, this is the 8-bit configuration data to be

sent to the ADC. When the ADCCON control bit in the SYSCON3

register = 1, this field determines the length of the ADC

configuration data held in the ADC Configuration Extension field

for sending to the ADC.

Frame Length:Frame length is the total number of shift clocks required to

complete a data transfer.

Default mode - Max148/9 = 25 (8 for configuration + 1 null bit +

16 bits result)

Extended mode - AD7811/12 = 23 (10 for configuration byte + 3

null + 10 result)

SMCKEN: Setting this bit will enable a free running clock at twice the

programmed ADC clock frequency to be output on the

SMPCLK

pin.

TXFRMEN: Setting this bit will cause an ADC data transfer to be initiated.

Value in ADC configuration field will be shifted out to the ADC

and depending on the frame length programmed, a number of

bits will be captured from the ADC. If the SYNCO register is

written to with the TXFRMEN bit low, no ADC transfer will take

place, but the Frame Length and the SMCKEN bits will be

affected.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

TXFRME

N

SMCKE

N

Frame Length

ADC Configuration Byte

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

ADC Configuration Extension

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

TXFRME

N

SMCKE

N

Frame Length

ADC Configuration Length