Ds1874 sfp+ controller with digital ldd interface – Rainbow Electronics DS1874 User Manual

Page 52

DS1874

SFP+ Controller with Digital LDD Interface

52

______________________________________________________________________________________

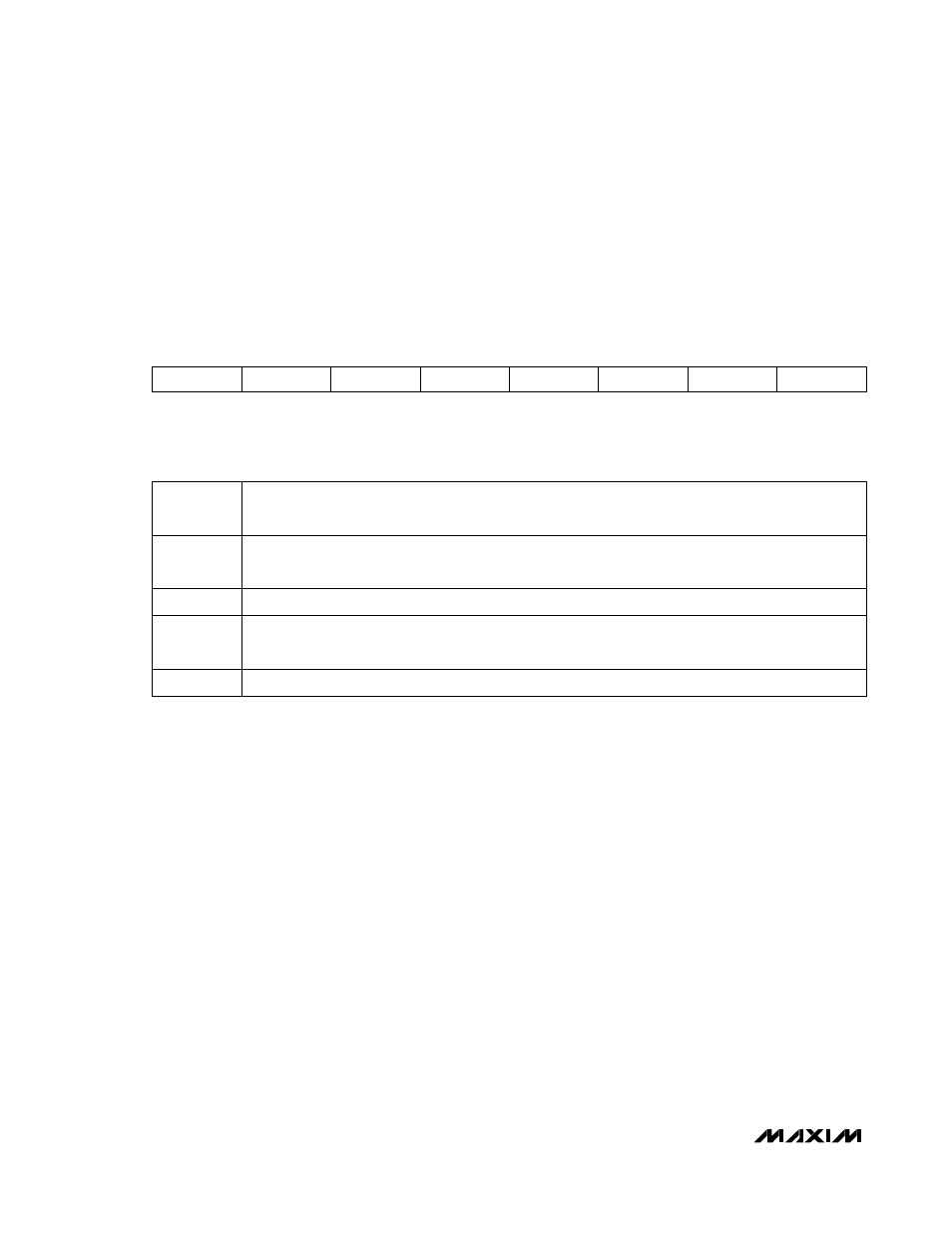

Table 01h, Register FBh: ALARM EN

0

POWER-ON

VALUE

00h

READ ACCESS

PW2 or (PW1 and RWTBL1C) or (PW1 and RTBL1C)

WRITE ACCESS

PW2 or (PW1 and RWTBL1C)

MEMORY TYPE

Nonvolatile (SEE)

FBh LOS

HI

LOS

LO RESERVED RESERVED BIAS

MAX RESERVED RESERVED RESERVED

BIT

7

BIT

0

Layout is identical to ALARM

1

in Lower Memory, Register 73h. The MASK bit (Table 02h, Register 89h) determines

whether this memory exists in Table 01h or 05h.

BIT

7

LOS HI: Enables alarm to create TXFINT (Lower Memory, Register 71h) logic.

0 = Disables interrupt from LOS HI alarm.

1 = Enables interrupt from LOS HI alarm.

BIT

6

LOS LO: Enables alarm to create TXFINT (Lower Memory, Register 71h) logic.

0 = Disables interrupt from LOS LO alarm.

1 = Enables interrupt from LOS LO alarm.

BITS

5:4

RESERVED

BIT

3

BIAS MAX: Enables alarm to create internal signal FETG (see Figure 12) logic.

0 = Disables interrupt from BIAS MAX alarm.

1 = Enables interrupt from BIAS MAX alarm.

BITS

2:0

RESERVED