Sftr (shift right), Sftr (shift right) -3 – IDEC MicroSmart User Manual

Page 247

13: S

HIFT

/ R

OTATE

I

NSTRUCTIONS

« FC4A M

ICRO

S

MART

U

SER

’

S

M

ANUAL

»

13-3

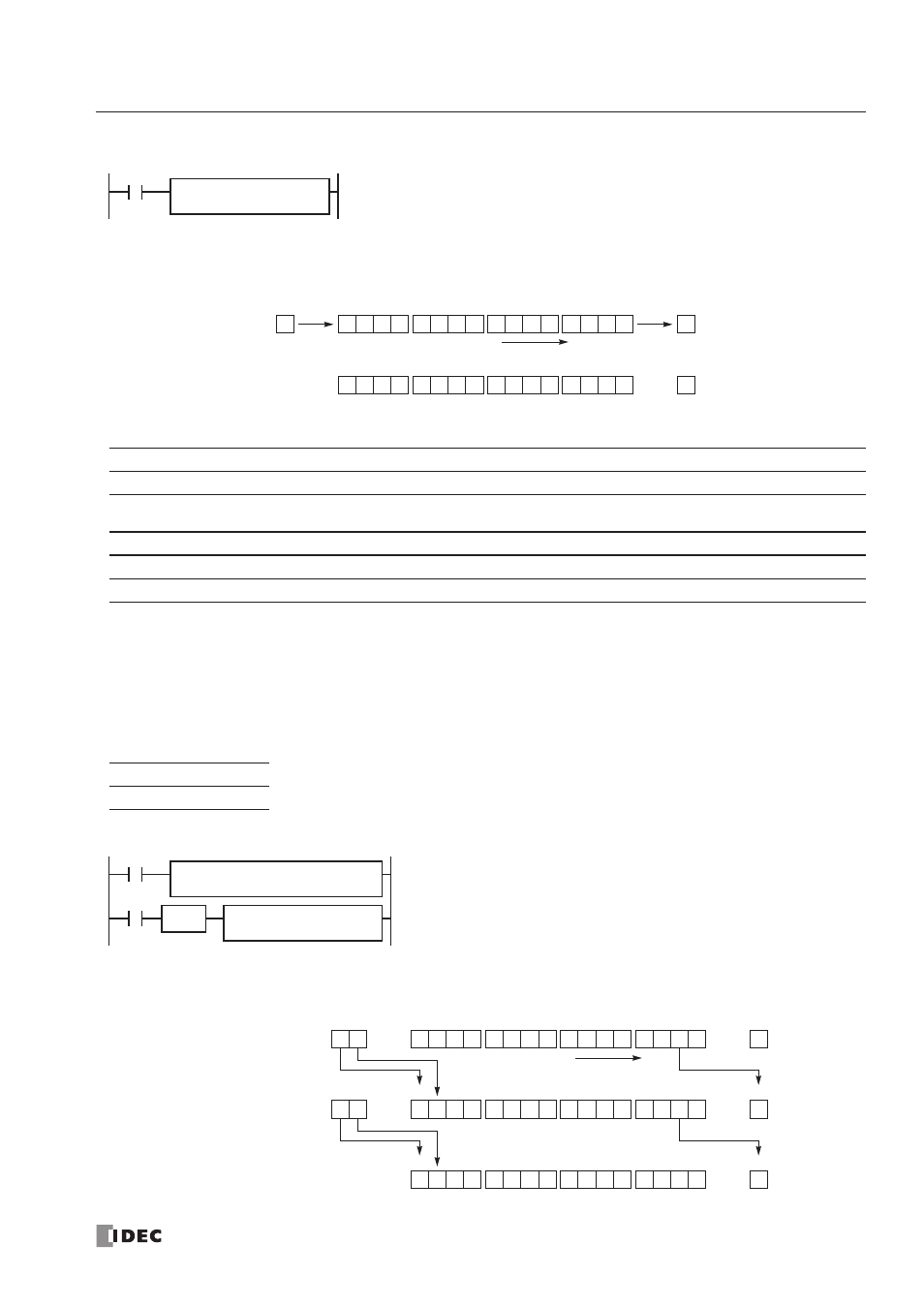

SFTR (Shift Right)

Applicable CPU Modules

Valid Operands

For the valid operand number range, see pages 6-1 and 6-2.

▲

Internal relays M0 through M1277 can be designated as S1. Special internal relays cannot be designated as S1.

The quantity of bits to shift can be 1 through 15.

Since the SFTR instruction is executed in each scan while input is on, a pulse input from a SOTU or SOTD instruction

should be used as required.

Valid Data Types

Example: SFTR

FC4A-C10R2/C

FC4A-C16R2/C

FC4A-C24R2/C

FC4A-D20K3/S3

FC4A-D20RK1/RS1 & FC4A-D40K3/S3

X

X

X

X

X

Operand

Function

I

Q

M

R

T

C

D

Constant

Repeat

S1 (Source 1)

Data for bit shift

—

X

▲ X — — X

—

—

bits

Quantity of bits to shift

—

—

—

—

—

—

—

1-15

—

W (word)

I (integer)

X

—

S1

*****

bits

**

S1

→ CY

When input is on, 16-bit data of the designated source operand S1 is shifted to

the right by the quantity of bits designated by operand bits.

The result is set to the source operand S1, and the last bit status shifted out is

set to a carr y (special internal relay M8003). Zeros are set to the MSB.

0

Before shift:

1

0

1

0

1

0

1

0 1

1

1

1

0

1

0

0

CY

M8003

MSB

LSB

S1

0

After shift:

1

1

1

1

0

0

0

0 1

1

0

0

1

0

1

1

CY

M8003

MSB

LSB

S1

Shift to the right

SFTR(W)

When

bits to shift = 1

When a bit operand such as Q (output), M (internal relay), or R (shift register) is designated

as the source, 16 points are used.

When a word operand such as D (data register) is designated as the source, 1 point is used.

M8120

REP

M8120 is the initialize pulse special internal relay.

When the CPU star ts operation, the MOV (move) instruction sets 29 to

data register D10.

Each time input I0 is turned on, 16-bit data of data register D10 is shifted

to the right by 2 bits as designated by operand bits. The last bit status

shifted out is set to a carr y (special internal relay M8003). Zeros are set

to the MSB.

SOTU

I0

S1 –

29

D1 –

D10

S1

D10

bits

2

SFTR(W)

MOV(W)

0

Before shift: D20 = 29

0

0

0

0

0

0

0

0 0

0

0

1

1

0

1

1

CY

M8003

MSB

LSB

D10

0

After first shift: D20 = 7

1

0

0

0

0

0

0

0 0

0

1

0

0

0

0

1

CY

M8003

MSB

LSB

D10

Bits to shift = 2

0

1

0

0

0

0

0

0

0 0

0

0

0

0

0

0

0

After second shift: D20 = 1

CY

M8003

MSB

LSB

D10

1

0

0

Shift to the right