Sundance SMT712 User Manual

Page 63

User Manual SMT712

Page 63 of 89

Last Edited: 11/12/2012 10:36:00

4.6.1.1.46

Clock Generator (AD9516-2) Register 0x191 – Divider0 –

0x164 (write).

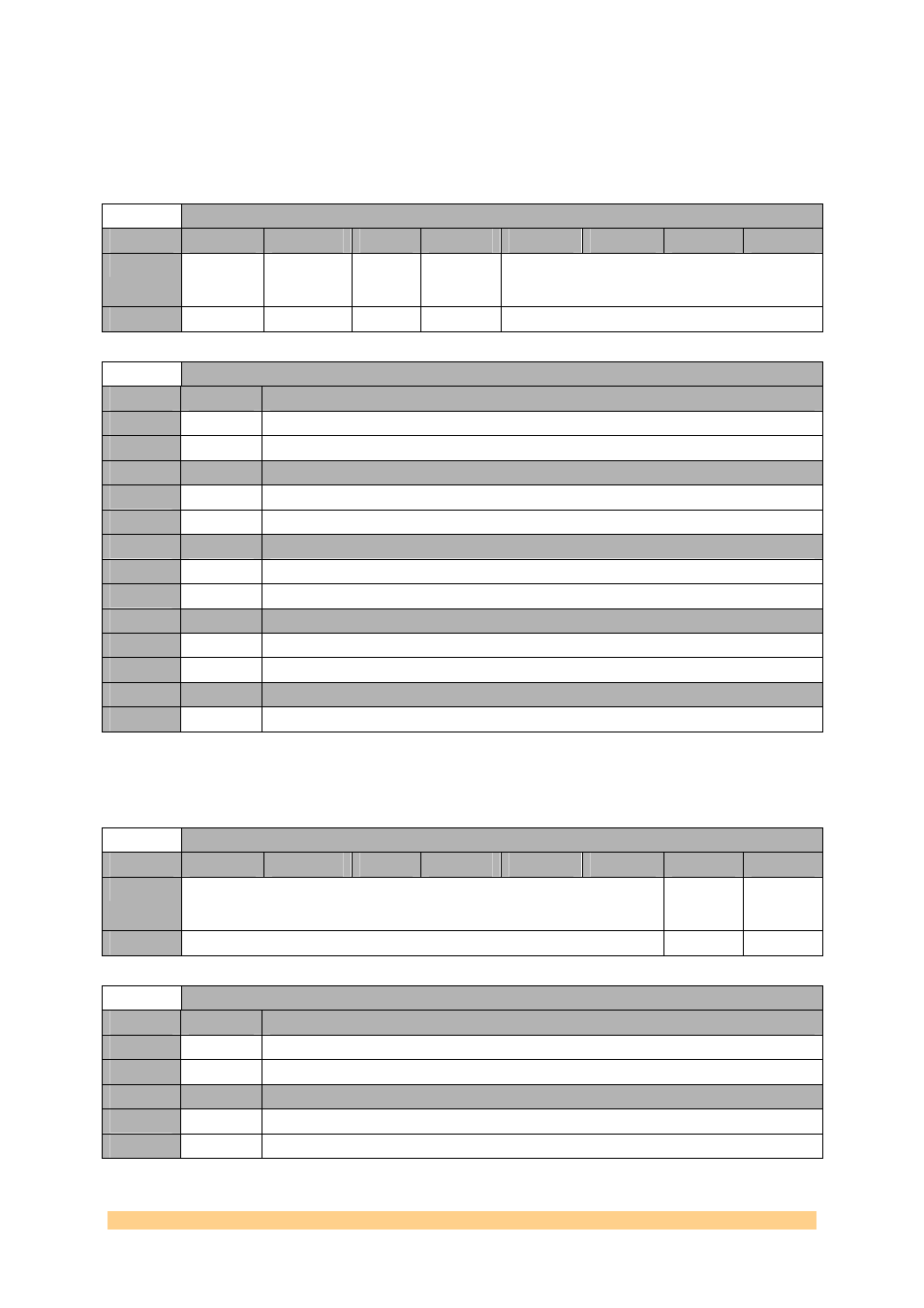

Clock Generator (AD9516-2) Register 0x191 – Divider0 – 0x164 (write)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Divider

bypass

Divider

Nosync

Divider

Force

High

Divider

Start High

Divider Phase Offset

Default

‘1’

‘0’

‘0’

‘0’

‘0000’

Clock Generator (AD9516-2) Register 0x191 – Divider0 – 0x164 (write)

Setting

Bit 7

Description (Divider Bypass)

0

0

use divider.

1

1

bypass divider.

Setting

Bit 6

Description (Divider Nosync)

0

0

obey chip-level SYNC signal.

1

1

ignore chip-level SYNC signal.

Setting

Bit 5

Description (Divider Force High)

0

0

divider output forced to low.

1

1

divider output forced to high.

Setting

Bit 4

Description (Divider Start High)

0

0

start low.

1

1

start high.

Setting

Bit 3..0

Description (REF2 Frequency Threshold)

0

0

Phase offset.

4.6.1.1.47

Clock Generator (AD9516-2) Register 0x192 – Divider0 –

0x168 (write).

Clock Generator (AD9516-2) Register 0x192 – Divder0 – 0x168 (write)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Divider

Direct to

Output

Divider

DCCOFF

Default

‘000000’

‘0’

‘0’

Clock Generator (AD9516-2) Register 0x192 – Divder0 – 0x168 (write)

Setting

Bit 1

Description (Divider Direct to Output)

0

0

VCO calibration not finished.

1

1

VCO calibration finished.

Setting

Bit 0

Description (Divider DCCOFF)

0

0

not in holdover.

1

1

holdover state active.