Sundance SMT712 User Manual

Page 42

User Manual SMT712

Page 42 of 89

Last Edited: 11/12/2012 10:36:00

4.6.1.1.14

Clock Generator (AD9516-2) Register 0x16 – PLL Control

1 – 0xE0 (write).

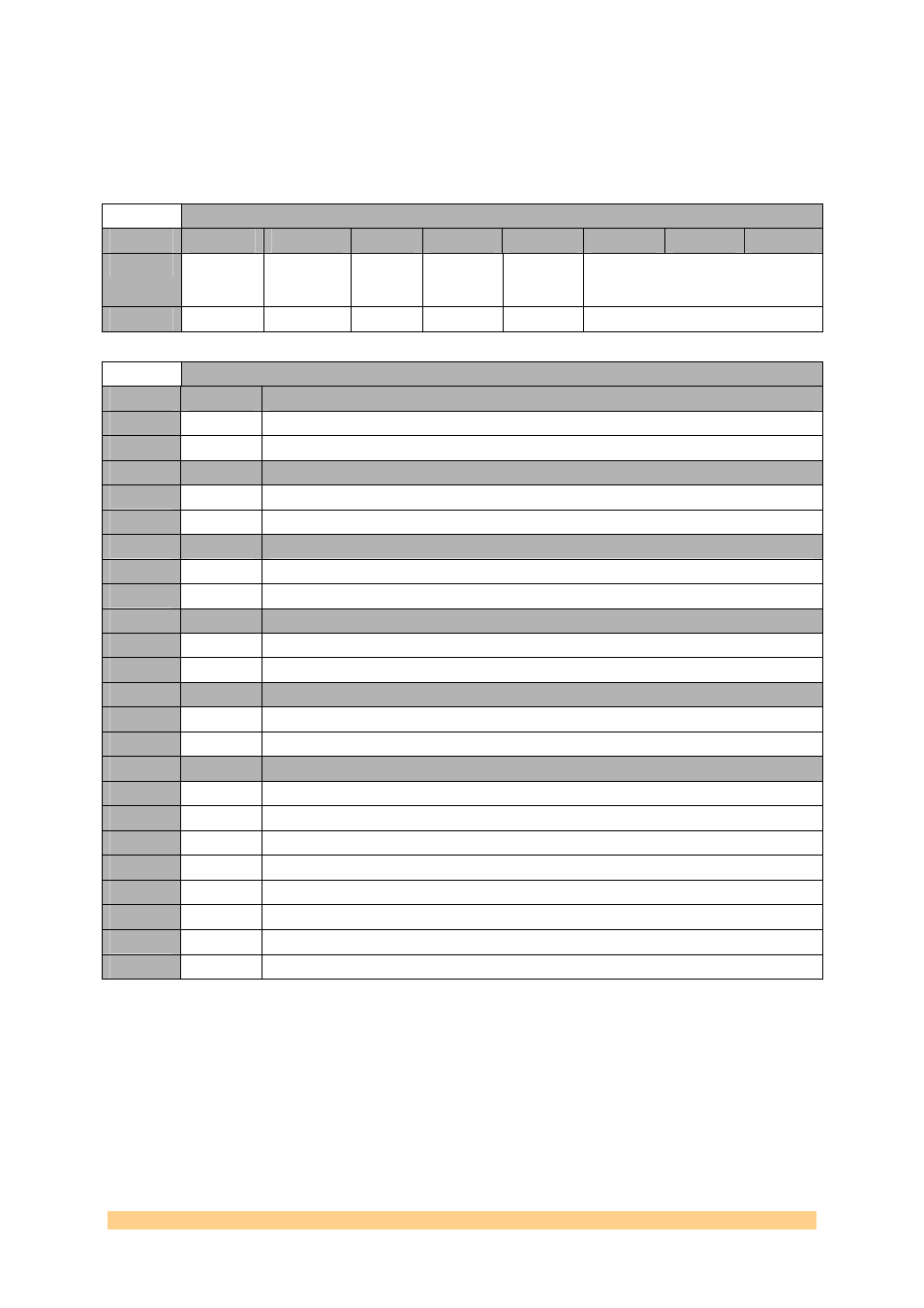

Clock Generator (AD9516-2) Register 0x16 – PLL Control 1 – 0xE0 (write)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Set CP Pin

to Vcp/2

Reset R

Counter

Reset A

and B

Counters

Reset All

Counters

B Counter

Bypass

Prescaler

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘110’

Clock Generator (AD9516-2) Register 0x16 – PLL Control 1 – 0xE0 (write)

Setting

Bit 7

Description (Set CP Pin to Vcp/2)

0

0

CP normal operation.

1

1

CP pin set to VCP/2.

Setting

Bit 6

Description (Reset R Counter)

0

0

Normal Mode of operation

1

1

reset R counter

Setting

Bit 5

Description (Reset A and B Counters)

0

0

Normal Mode of operation

1

1

reset A and B counters.

Setting

Bit 4

Description (Reset all Counters)

0

0

Normal Mode of operation

1

1

reset R, A, and B counters.

Setting

Bit 3

Description (B Counter Bypass)

0

0

Normal mode of operation

1

1

B counter is set to divide-by-1.

Setting

Bit 2..0

Description (Prescaler)

7

111

FD Divide-by-3.

6

110

DM Divide-by-32 and divide-by-33 when A!=0; divide-by-32 when A = 0.

5

101

DM Divide-by-16 and divide-by-17 when A!=0; divide-by-16 when A = 0.

4

100

DM Divide-by-8 and divide-by-9 when A!=0; divide-by-8 when A = 0.

3

011

DM Divide-by-4 and divide-by-5 when A!=0; divide-by-4 when A=0.

2

010

DM Divide-by-2 and divide-by-3 when A!=0; divide-by-2 when A=0.

1

001

FD Divide-by-2.

0

000

FD Divide-by-1.