Sundance SMT712 User Manual

Page 34

User Manual SMT712

Page 34 of 89

Last Edited: 11/12/2012 10:36:00

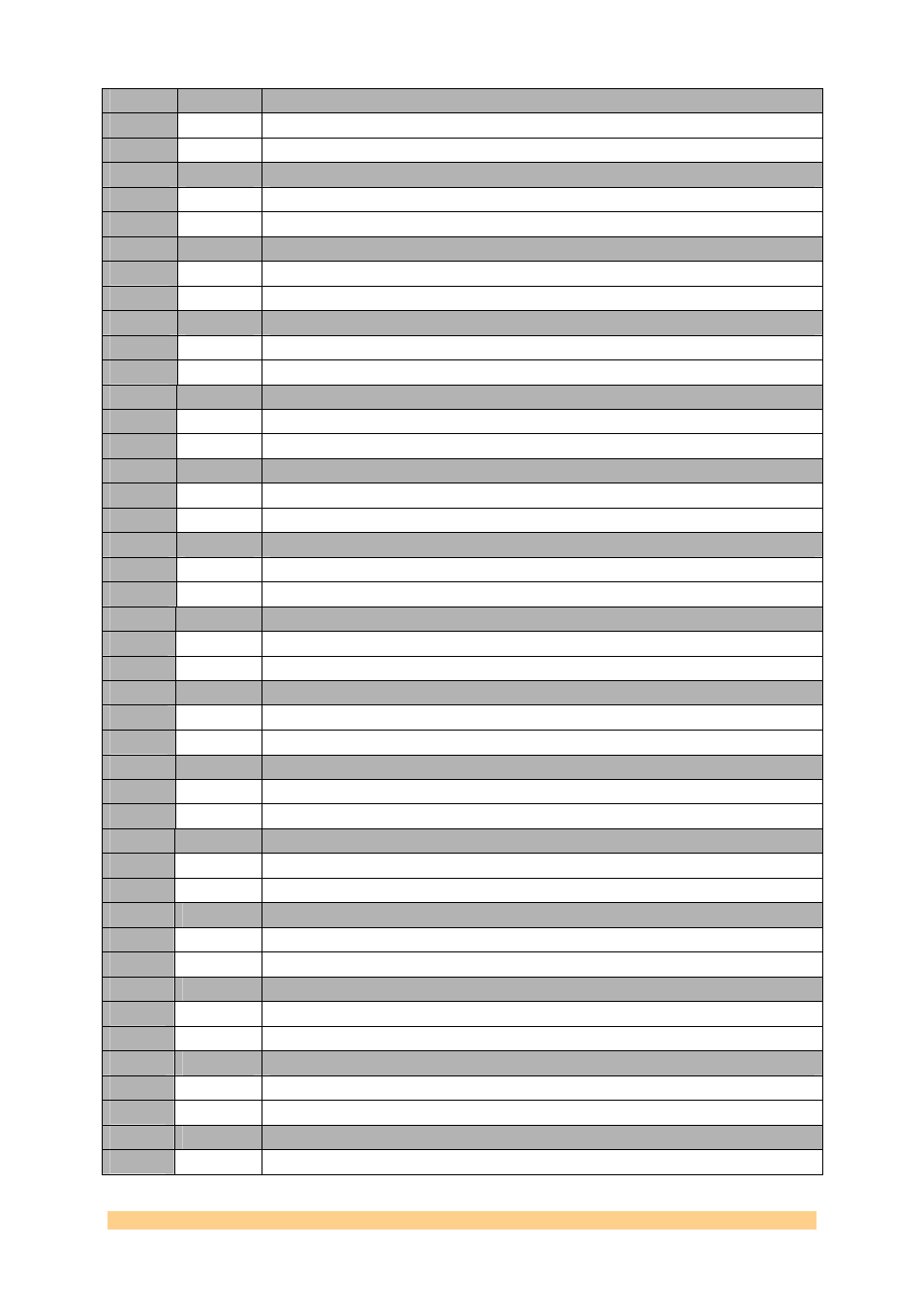

Setting

Bit 11

Description – Clock Chip Lock Detect Pin.

0

0

Programmable pin. See AD9516-2 register settings.

1

1

Programmable pin. See AD9516-2 register settings.

Setting

Bit 13

Description – DDR2 phy init done. Memory Bank A.

0

0

A problem occurred or Memory Bank A is kept in reset.

1

1

Normal Mode of Operation.

Setting

Bit 15

Description – DDR2 fifo empty. Memory Bank A.

0

0

DDR2 fifo contains samples.

1

1

DDR2 fifo is empty.

Setting

Bit 16

Description – DACA Synchronisation Reference State.

0

0

DACA reference clock at a logical ‘0’ level.

1

1

DACA reference clock at a logical ‘1’ level.

Setting

Bit 17

Description – DACB Synchronisation Reference State.

0

0

DACB reference clock at a logical ‘0’ level.

1

1

DACB reference clock at a logical ‘1’ level.

Setting

Bit 18

Description – DDR2 phy init done. Memory Bank B.

0

0

A problem occurred or Memory Bank B is kept in reset.

1

1

Normal Mode of Operation.

Setting

Bit 20

Description – DDR2 fifo empty. Memory Bank B.

0

0

DDR2 fifo contains samples.

1

1

DDR2 fifo is empty.

Setting

Bit 23

Description – DDR2 Fifo Full. Memory Bank A

0

0

Memory bank A not full.

1

1

Memory bank A full.

Setting

Bit 24

Description – DDR2 Fifo Full. Memory Bank B

0

0

Memory bank B not full.

1

1

Memory bank B full.

Setting

Bit 25

Description – DDR2 Fifo almost empty. Memory Bank A

0

0

Memory bank A not almost empty.

1

1

Memory bank A almost empty.

Setting

Bit 26

Description – DDR2 Fifo almost empty. Memory Bank B

0

0

Memory bank B not almost empty.

1

1

Memory bank B almost empty.

Setting

Bit 27

Description – System Monitor – FPGA Die Temperature Alarm

0

0

Normal Mode of Operation.

1

1

Upper die temperature threshold reached.

Setting

Bit 28

Description – System Monitor – Vccint Alarm

0

0

Normal Mode of operation.

1

1

Upper Vccint threshold reached.

Setting

Bit 29

Description – System Monitor – Vccaux Alarm

0

0

Normal Mode of Operation.

1

1

Upper Vccaux threshold reached.

Setting

Bit 30

Description – System Monitor – Over Temperature Alarm

0

0

Normal Mode of Operation.