1 register descriptions, 1 general control register – 0x08 (read-only) – Sundance SMT712 User Manual

Page 32

User Manual SMT712

Page 32 of 89

Last Edited: 11/12/2012 10:36:00

0x1A4

Clock Generator (AD9516-2) register 0x1A1 –

Divider4

Read-back (FPGA Register) Clock Generator

(AD9516-2) register 0x1A1 – Divider4

0x1A8

Clock Generator (AD9516-2) register 0x1A2 –

Divider4

Clock Generator (AD9516-2) register 0x1A2 –

Divider4

0x1AC

Clock Generator (AD9516-2) register 0x1E0 – VCO

Divider

Read-back (FPGA Register) Clock Generator

(AD9516-2) register 0x1E0 – VCO Divider

0x1B0

Clock Generator (AD9516-2) register 0x1E1 –

Input CLKs

Read-back (FPGA Register) Clock Generator

(AD9516-2) register 0x1E1 – Input CLKs

0x1B4

Clock Generator (AD9516-2) register 0x230 –

Power-down and Sync

Read-back (FPGA Register) Clock Generator

(AD9516-2) register 0x230 – Power-down and Sync

0x1B8

Clock Generator (AD9516-2) register 0x232 –

Update all registers

Read-back (FPGA Register) Clock Generator

(AD9516-2) register 0x232 – Update all registers

0x1C0

System Monitor upper and lower FPGA Die

Temperature thresholds

System Monitor – Read-back FPGA max and min

die temperature measured

0x1C4

System Monitor upper and lower FPGA Vccint

(Core Voltage) upper and lower thresholds

System Monitor – Read-back FPGA max and min

Vccint (Core Voltage) measured

0x1C8

System Monitor upper and lower FPGA Vccaux

(Core Voltage) upper and lower thresholds

System Monitor – Read-back FPGA max and min

Vccaux (Core Voltage) measured

0x1CC

DDS (DACA) Frequency Register

0x1D0

DDS (DACB) Frequency Register

0x1D4

DACA DCM Phase Shifts.

Reserved.

0x1D8

DACB DCM Phase Shifts.

Reserved.

0x1DC

DACA Pattern Size.

Reserved.

0x1E0

DACB Pattern Size.

Reserved.

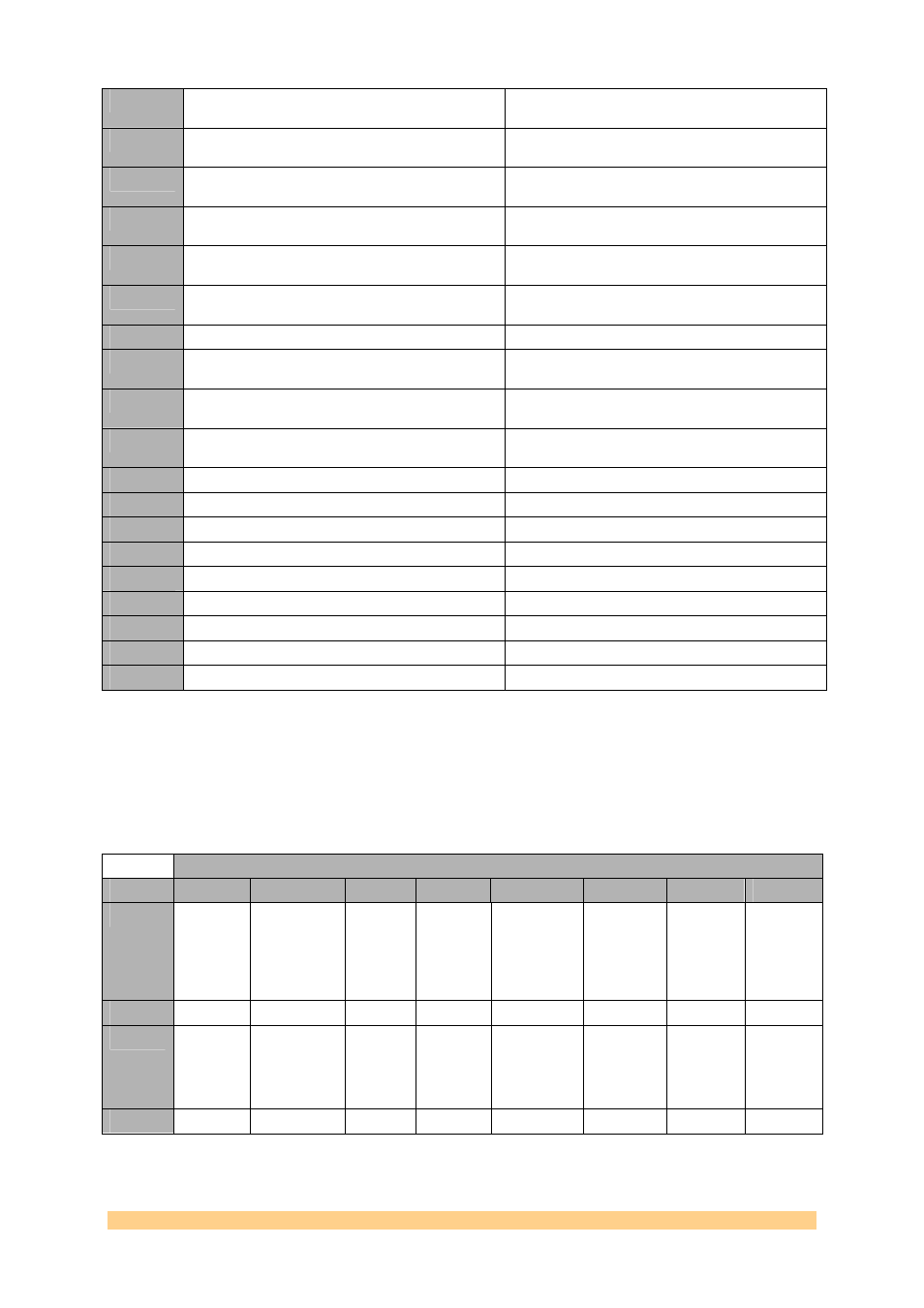

Figure 15 – Register Memory Map.

4.6.1.1

Register Descriptions

4.6.1.1.1

General Control Register – 0x08 (read-only).

Offset 0x0400 –

General control Register – 0x08 (Read-only register).

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

3

DACA or

DACB

DCM

Busy

status

System

Monitor –

Over

Temperature

alarm

System

Monitor

– Vccaux

alarm

System

Monitor –

Vccint

alarm

System

Monitor –

Die

temperature

alarm

DDR2 Fifo

Almost

Empty

(Memory

Bank B)

DDR2

Fifo

Almost

Empty

(Memory

Bank A)

DDR2

Fifo Full

(Memory

Bank B)

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

2

DDR2

Fifo Full

(Memory

Bank A)

DDR2

Fifo

empty

(Memory

Bank B)

DDR2 phy

init done

(Memory

Bank B)

DACB

Synch

Reference

State

DACA

Synch

Reference

State

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’