Sundance SMT712 User Manual

Page 36

User Manual SMT712

Page 36 of 89

Last Edited: 11/12/2012 10:36:00

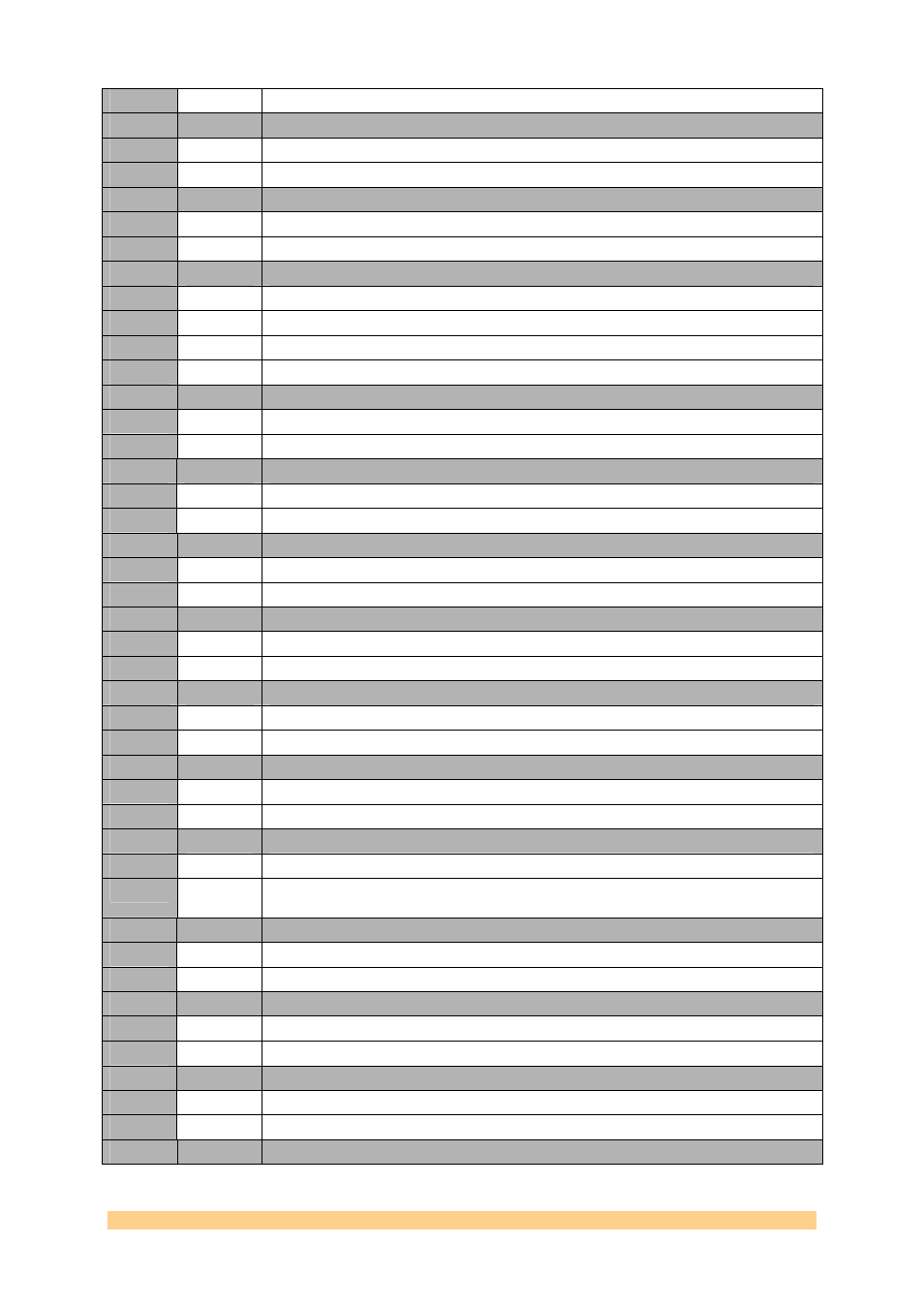

1

1

DACB under power.

Setting

Bit 6

Description – Clock power supply.

0

0

Clock chip not powered.

1

1

Clock chip under power.

Setting

Bit 7

Description – Sampling Clock Source Selection

0

0

ADCs are clocked using the on-board clock synthesizer.

1

1

ADCs are clocked using an external source.

Setting

Bit 9-8

Description – Reference Clock Selection

0

00

External Reference Selected.

1

01

100-MHz PXI Express Reference Clock.

2

10

10-MHz PXI Express Reference Clock.

3

11

100-MHz PXI Express Reference Clock.

Setting

Bit 10

Description – Reference Clock Circuitry Reset

0

0

Normal Mode of Operation.

1

1

Reference Clock Circuitry kept in Reset (Default).

Setting

Bit 11

Description – Soft Reset

0

0

Normal Mode of Operation

1

1

Resets Xlinks blocks – usually used before starting an acquisition to clear Xlinks FIFOs.

Setting

Bit 12

Description – Reference Clock Out Divider.

0

0

Divide by 1.

1

1

Divide by 2.

Setting

Bit 13

Description – On-board Reference Clock Divider

0

0

Divide by 1.

1

1

Divide by 2.

Setting

Bit 14

Description – On-board Clock Reset.

0

0

Normal mode of operation.

1

1

On-board Clock chip in reset mode.

Setting

Bit 15

Description – On-board Clock Synch (active low).

0

0

1

1

Setting

Bit 17

Description – Trigger Source Selection

0

0

On-board trigger selected (bit 16)

1

1

External trigger selected (Trig Input). A Level ‘high’ on the Trig Input is required to start

an acquisition (length of the pulse being at least 1/8

th

of the ADC sampling clock.

Setting

Bit 19

Description – DDR2 Reset

0

0

Normal Mode of Operation

1

1

Keeps DDR2 circuitry in Reset

Setting

Bit 20

Description – SHB1 Reset

0

0

Normal Mode of Operation

1

1

Keeps SHB1 circuitry in Reset

Setting

Bit 21

Description – SHB2 Reset

0

0

Normal Mode of Operation

1

1

Keeps SHB2 circuitry in Reset

Setting

Bit 24

Description Force DACA DCM to Reset (Auto-Clear).