Sundance SMT712 User Manual

Page 58

User Manual SMT712

Page 58 of 89

Last Edited: 11/12/2012 10:36:00

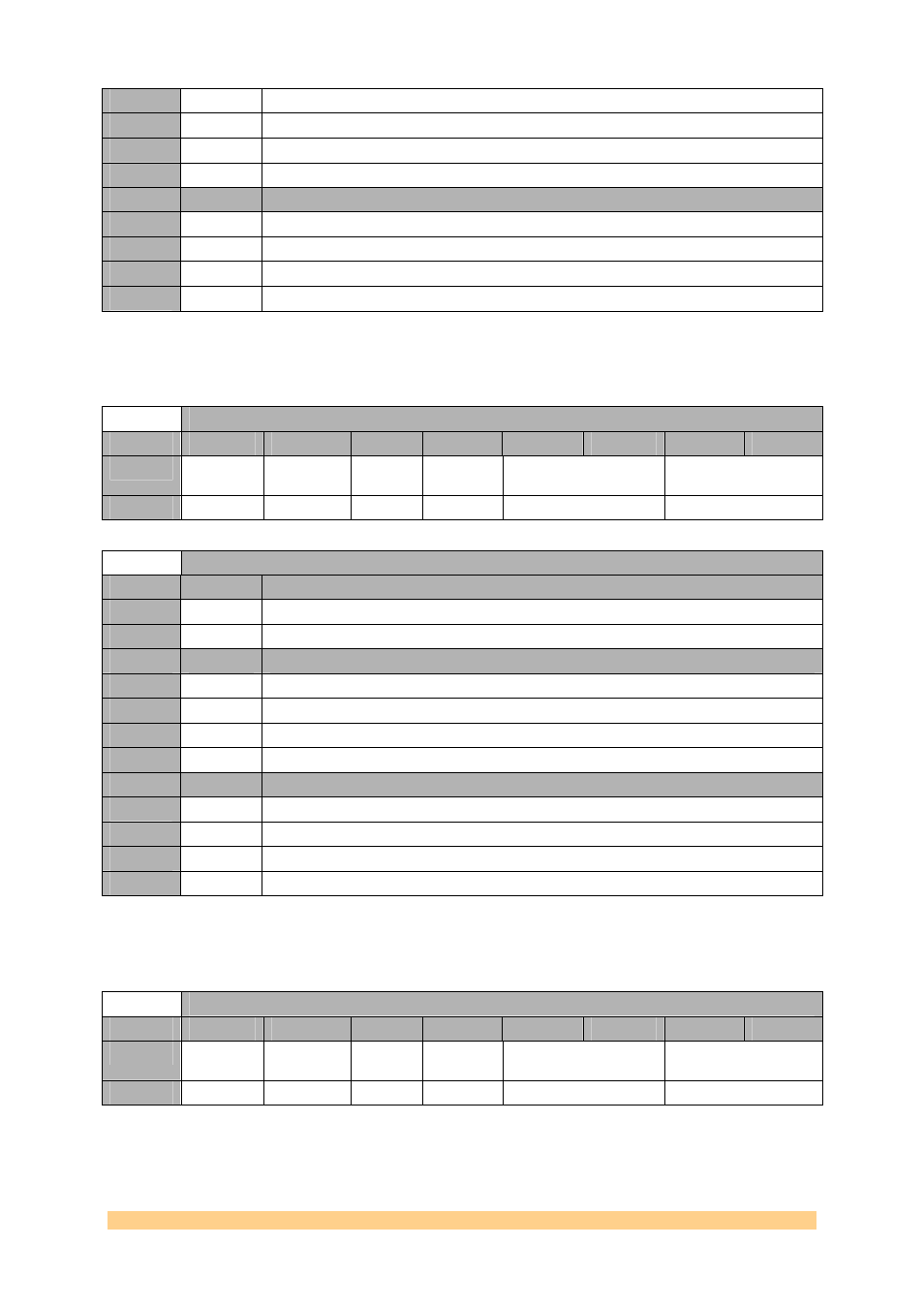

3

‘11’

960

2

‘10’

780

1

‘01’

600

0

‘00’

400

Setting

Bit 1..0

Description (OUT3 Power-down)

3

‘11’

Total power-down, reference off; use only if there are no external load resistors. Off.

2

‘10’

Partial power-down, reference on, safe LVPECL power-down.

1

‘01’

Partial power-down, reference on; use only if there are no external load resistors.

0

‘00’

Normal operation.

4.6.1.1.39

Clock Generator (AD9516-2) Register 0xF4 – OUT4 –

0x148 (write).

Clock Generator (AD9516-2) Register 0xF4 – OUT4 – 0x148 (write)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Reserved

Reserved

OUT4

Invert

OUT4 LVPECL

Differential Voltage

OUT4 Power-down

Default

‘0’

‘0’

‘0’

‘0’

‘10’

‘00’

Clock Generator (AD9516-2) Register 0xF4 – OUT4 – 0x148 (write)

Setting

Bit 4

Description (OUT4 Invert)

0

0

noninverting.

1

1

inverting.

Setting

Bit 3..2

Description (OUT4 LVPECL Differential Voltage - (VOD - mV))

3

‘11’

960

2

‘10’

780

1

‘01’

600

0

‘00’

400

Setting

Bit 1..0

Description (OUT4 Power-down)

3

‘11’

Total power-down, reference off; use only if there are no external load resistors. Off.

2

‘10’

Partial power-down, reference on, safe LVPECL power-down.

1

‘01’

Partial power-down, reference on; use only if there are no external load resistors.

0

‘00’

Normal operation.

4.6.1.1.40

Clock Generator (AD9516-2) Register 0xF5 – OUT5 –

0x14C (write).

Clock Generator (AD9516-2) Register 0xF5 – OUT5 – 0x14C (write)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Reserved

Reserved

OUT5

Invert

OUT5 LVPECL

Differential Voltage

OUT5 Power-down

Default

‘0’

‘0’

‘0’

‘0’

‘10’

‘10’