Sundance SMT712 User Manual

Page 33

User Manual SMT712

Page 33 of 89

Last Edited: 11/12/2012 10:36:00

1

DDR2

Fifo

empty

(Memory

Bank A)

DDR2

phy init

done

(Memory

Bank A)

Clock Chip

Lock Detect

Pin

Clock Chip

Reference

Monitoring

Pin

Clock

Chip

Status Pin

XOR

Synch

Reference

State

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘1’

‘0’

0

PCI32

Idelay

ready

Iodelay

clock

(200mhz)

locked

DACb

DCM

Lock

Status

DACa

DCM

Lock

Status

Iodelay

Ready ddr2

chb

Iodelay

ready ddr2

cha

lock dcm

ddr2 chb

lock dcm

ddr2 cha

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

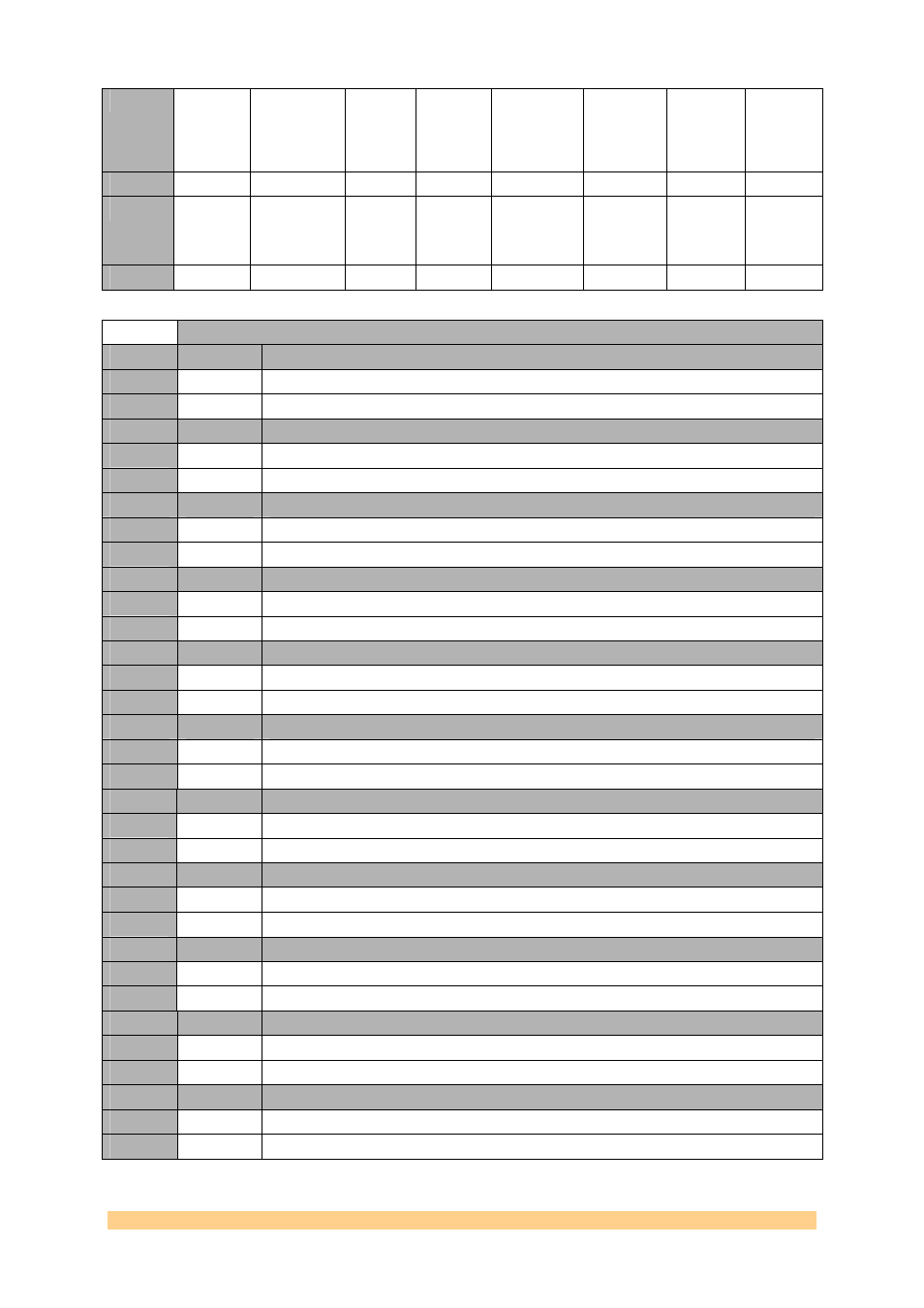

Offset 0x0400 –

General control Register – 0x08 (Read-only register).

Setting

Bit 0

Description – DCM Lock Status DDR2 BankA

0

0

DCM generating clock for DDR2 bank A not locked.

1

1

DCM generating clock for DDR2 bank A locked – normal mode of operation.

Setting

Bit 1

Description – DCM Lock Status DDR2 BankB

0

0

DCM generating clock for DDR2 bank B not locked.

1

1

DCM generating clock for DDR2 bank B locked – normal mode of operation.

Setting

Bit 2

Description – IoDelay Ready DDR2 BankA

0

0

IoDelays not ready.

1

1

IoDelays ready. Normal Mode of operation.

Setting

Bit 3

Description – IoDelay Ready DDR2 BankB

0

0

IoDelays not ready.

1

1

IoDelays ready. Normal Mode of operation.

Setting

Bit 4

Description – DACA DCM Lock Status.

0

0

DCM DACA not locked.

1

1

DCM DACA Locked. Normal Mode of Operation.

Setting

Bit 5

Description – DACB DCM Lock Status.

0

0

DCM DACB not locked.

1

1

DCM DACB Locked. Normal Mode of Operation.

Setting

Bit 6

Description – Lock Status PCI IoDelay Clock

0

0

DCM IoDelay clock - PCI interface - not locked.

1

1

DCM IoDelay clock - PCI interface - locked. Normal Mode of Operation.

Setting

Bit 7

Description – IoDelays PCI Interface Ready

0

0

IoDelays PCI Interface not ready.

1

1

IoDelays PCI Interface ready. Normal Mode of operation.

Setting

Bit 8

Description – XOR Synchronisation Reference State

0

0

DACA and DACB reference clocks are at the same levels. Either both ‘0’ or both ‘1’.

1

1

DACA and DACB reference clocks are at opposite levels. One is ‘0’ and the other is ‘1’.

Setting

Bit 9

Description – Clock Chip Status Pin.

0

0

Programmable pin. See AD9516-2 register settings.

1

1

Programmable pin. See AD9516-2 register settings.

Setting

Bit 10

Description – Clock Chip Reference Monitoring Pin.

0

0

Programmable pin. See AD9516-2 register settings.

1

1

Programmable pin. See AD9516-2 register settings.