5 post, Post, Intelligent peripheral management controller – Artesyn ATCA-8330 Installation and Use (April 2015) User Manual

Page 166

Intelligent Peripheral Management Controller

ATCA-8330 Installation and Use (6806800S82B)

166

7.5

POST

POST is executed at IPMC startup when either a hard (blade physically extracted/reinserted) or

cold (IPMI Command) reset is performed. POST verifies the functionality of SRAM, IPMB-0,

EEPROM data storage, FRU-Information, and all devices (primarily sensors) attached to the

IPMC's private master-only I

2

C bus. A detailed description of POST tests are as follows:

1. FRU-Information - This test verifies that the FRU-Information is readable from the external

EEPROM where it is stored. Once read, each section's checksum is computed and

validated.

2. IPMB-0 - This test reads the ready signals coming from the I

2

C buffers. This test passes as

long as both ready signals are active and both IPMB busses (IPMB-A and IPMB-B) are

enabled.

3. EEPROM - This test verifies that the EEPROM contents are readable via I

2

C. Since the IPMC

stores its runtime and persistent data here, proper operation is crucial.

4. Master-Only I2C - This test verifies that all expected devices attached to the master-only

I2C bus are accessible.

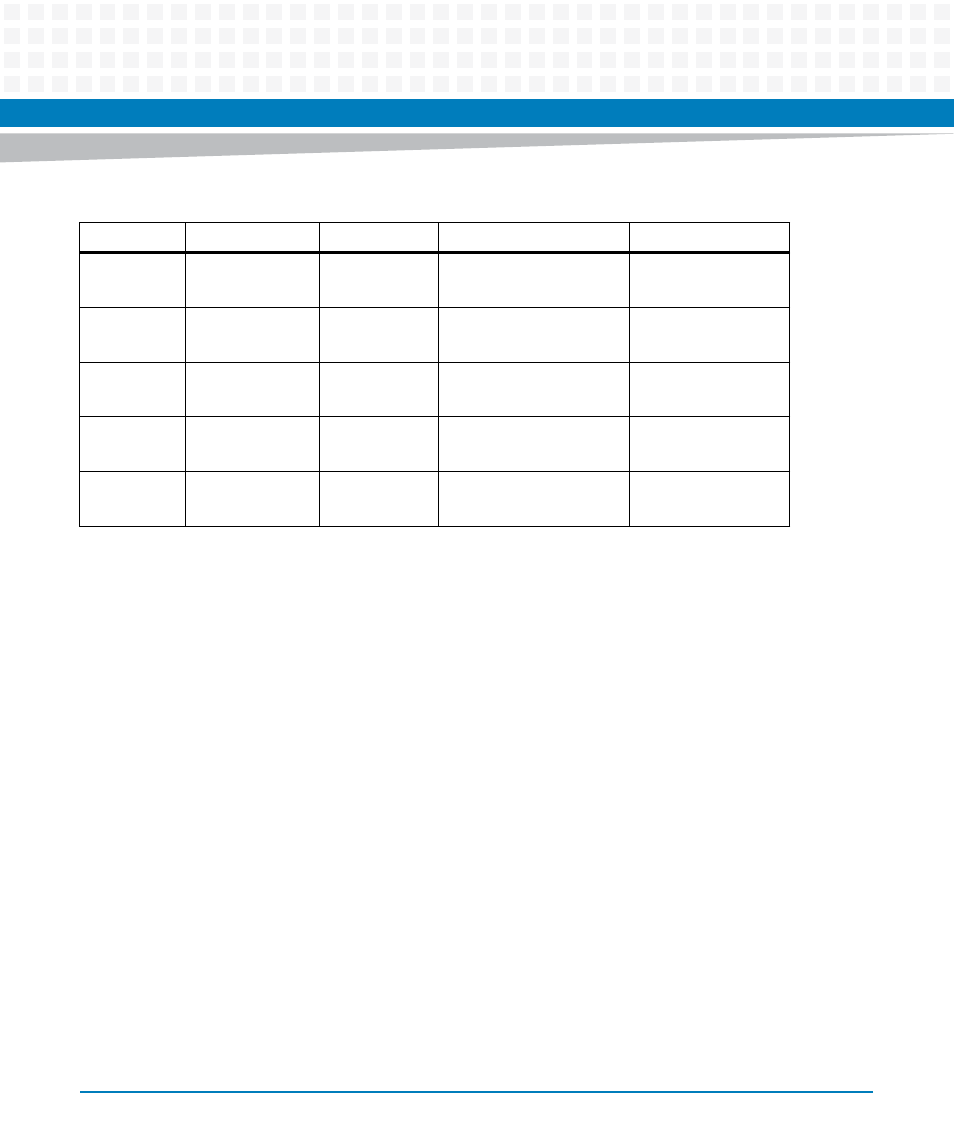

0xA6

IPMC private #4

FRU #6

DIMM 5 temp

DSP [20,23]

24C02

0xA8

IPMC private #4

FRU #7

DIMM 6 temp

DSP [24,27]

24C02

0xAA

IPMC private #4

FRU #8

DIMM 7 temp

DSP [28,31]

24C02

0xAC

IPMC private #4

FRU #9

DIMM 8 temp

DSP [32,35]

24C02

0xAE

IPMC private #4

FRU #10

DIMM 9 temp

DSP [36,39]

24C02

Table 7-4 Voltage and Temperature Sensor Devices (continued)

I2C address

I2C bus

Domain

Purpose

Device