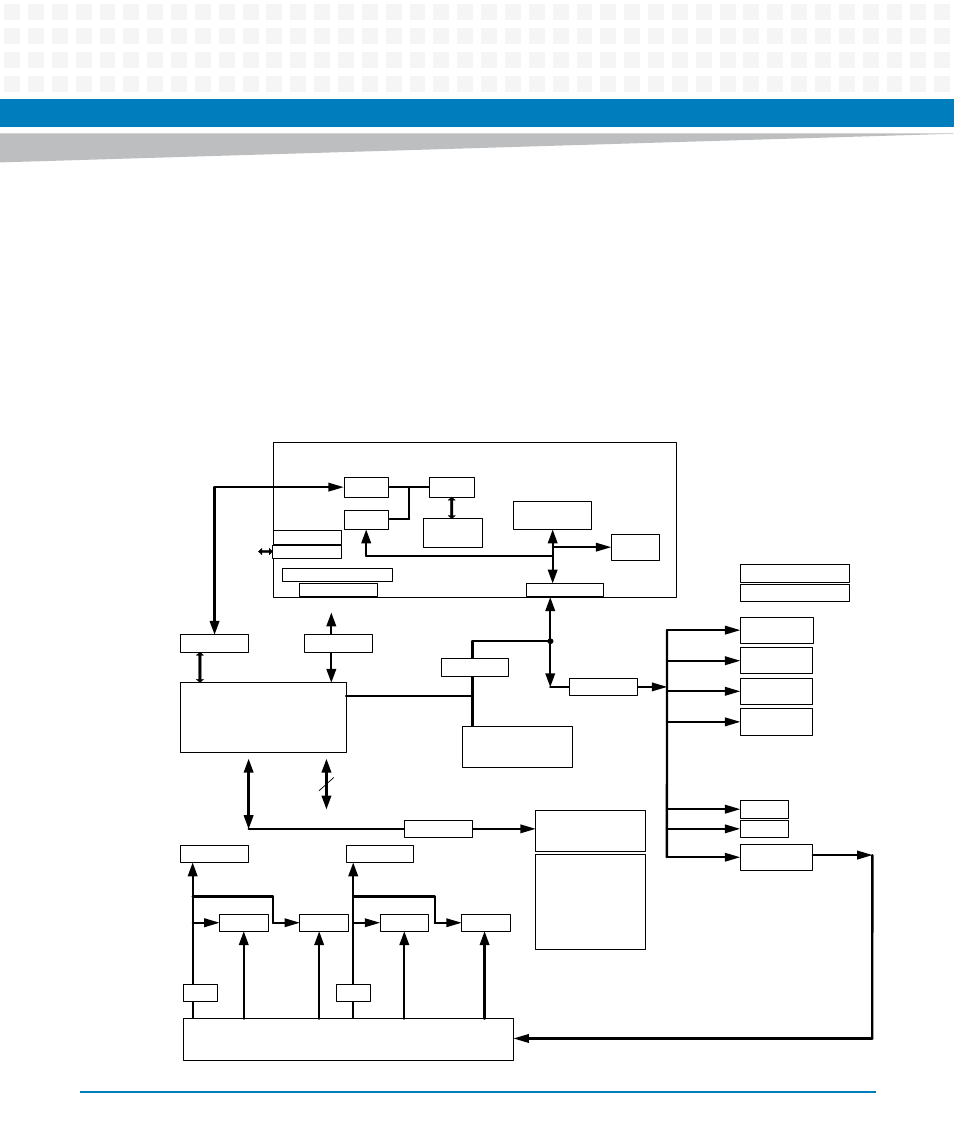

Figure 5-7, Smbus architecture, Functional description – Artesyn ATCA-8330 Installation and Use (April 2015) User Manual

Page 125: Cpu 0, Ipmc, Intel cavecreek pch

Functional Description

ATCA-8330 Installation and Use (6806800S82B)

125

The Master SMBus interface of the Intel DH8900CC PCH is connected to on-board devices like

Clock PLLs, temperature sensors and so on. An I2C Bus Repeater of type PCA9515 is used for

load distribution and buffering.

Additionally, the CPU provides 2x SMBuses to connect to the SPD PROMs of the DDR3 memory

system. Two I2C Bus Level Translators of type PCA9517A are used for voltage level translation

to buffer the SMBus portion going to the SPD PROMs on the DIMM.

The following figure shows the ATCA-8330 SMBus architecture.

Figure 5-7

SMBus Architecture

SMT3

CPU 0

SMB_DAT

SMT1

ME

Thermal

Sensors

Host SMB

Master/Slave

TCO

Slave

EP Slave

EP_SMBus

IPMI Packets (GbE)

GbE_SMBus

MST_SMBus

Isolation

Iso +3.3V

Isolation

PCA9515

Mellanox MT27514

Mellanox MT27514

PCH 0xE0

LM75 Base

0x90

MAX6618

PECI HUB

IPMC

CK420BQ

DB1900Z

XDP0

XDP1

5x DSP DIMM

0xA6,A8,AA,AC,AE

0x36,38,3A,3C,3E

5x DSP DIMM

0xA6,A8,AA,AC,AE

0x36,38,3A,3C,3E

LM75 Bot 0x90

LM75 Top 0x92

PIM 0x5E

CPLD0xFE

24C02 SEL 0xA6-

>A4

24C02 FRU

0xA4->A2

PCA9515

ISL90727

ISL90727

DIMM0

DIMM0

DIMM0

DIMM0

LS

SMB_CLK

I2C Bus #3 (SOL) I2C #3

I2C Bus #1

(H8S: P82, P83)

Private IPMB

I2C Bus #4

IPMB-A/B

I2C Bus #2, #3

CPU0_DDR_SC()L0

CPU0_DDR_SDA0

CPU0_DDR_SCL1

CPU0_DDR_SDA1

LS

Ch 0 (A)

Ch 1 (B)

Ch 2 (C)

Ch 3 (D)

A 0h

A 8h

A 0h

A 8h

Intel Cavecreek PCH

IPMB-L (I2C#5)

2

PECI 3.0

PECI 3.0

PECI 3.0