4 boot controller, 5 dsp configuration, 4 boot controller 5.4.1.5 dsp configuration – Artesyn ATCA-8330 Installation and Use (April 2015) User Manual

Page 107: Table 5-1, Ethernet physical interface mapping, Table 5-2, Dsp control signals, Functional description

Functional Description

ATCA-8330 Installation and Use (6806800S82B)

107

Variety of flexible address filtering modes

IEEE 802.1Q VLAN tag detection for reception frames

Network statistics with RMON/MIB counters (RFC 2819 / RFC 2665)

First module also has a 40MHz Station Management Interface (SMA or MDIO interface).

5.4.1.4

Boot Controller

The boot controller is responsible for managing the boot process. The boot process loads a

boot image, which is created by Octasic software tool. This allows the user to specify optional

device configuration and the application image to load.

The boot process uses a default device configuration determined by either a “lowest common

capability” and/or the BOOT_MODE to load a boot image. The final device configuration

information is obtained from the boot image and can override the one used for the boot

process.

The ATCA-8330 Stirling card is configured for BOOTP on EMAC 2 on SERDES 2 (SGMII, 1Gbps).

Note: The OCT2224M does not need a FLASH device to boot; it can boot using DHCP/TFTP to

download its image and configuration.

5.4.1.5

DSP Configuration

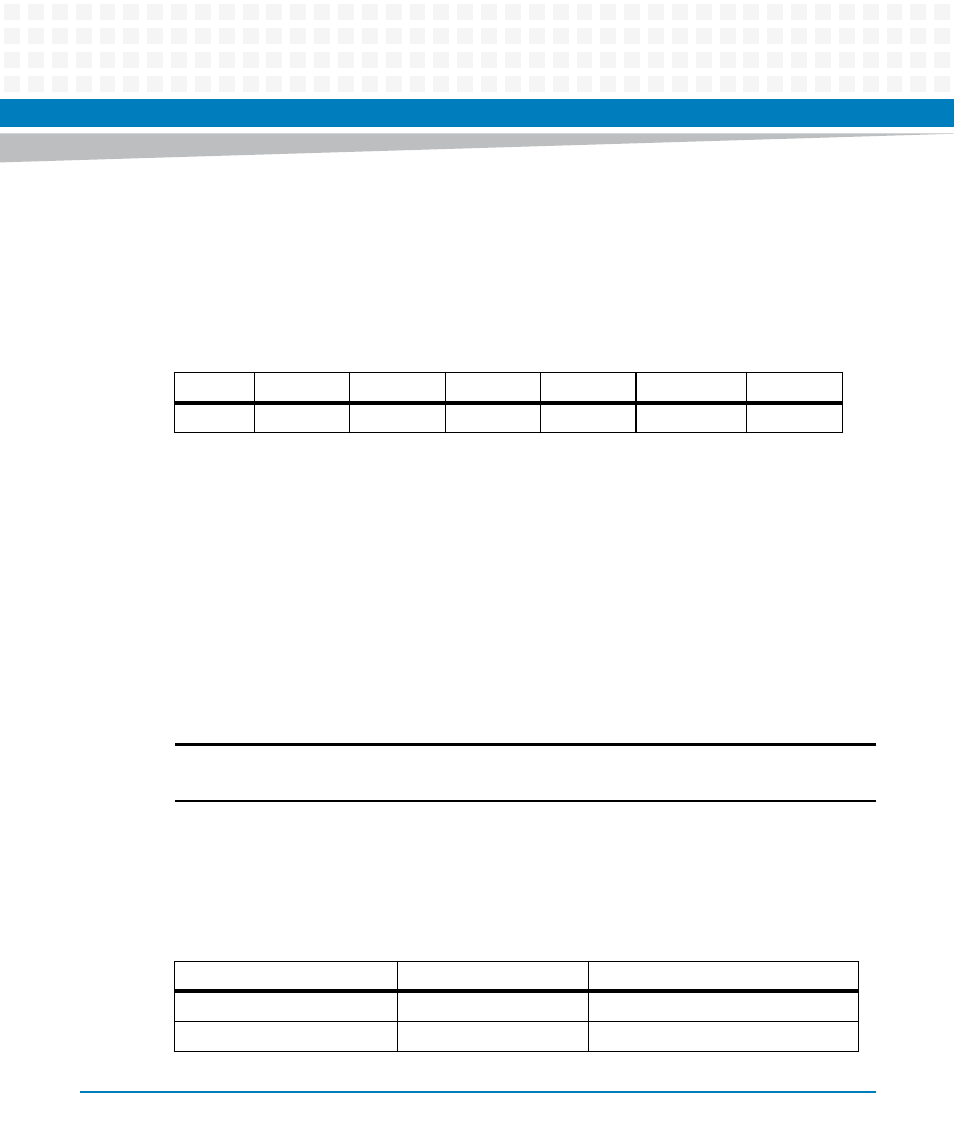

The following table lists the assignment of the DSP control and configuration pins.

Table 5-1 Ethernet Physical Interface Mapping

Mode

SERDES 0

SERDES 1

SERDES 2

SERDES 3

Eth 0

Eth 1

5

EMAC 1

EMAC 3

EMAC 2

EMAC 0

n/a

n/a

Table 5-2 DSP Control Signals

Signal Group

Controlled by

Description

DSPx_RST_N

DSP-FPGA

Reset Input to each DSP

DSPx_INT_N

DSP-FPGA

Interrupt Output from each DSP