19 real time clock, 20 smbus, 19 real time clock 5.20 smbus – Artesyn ATCA-8330 Installation and Use (April 2015) User Manual

Page 124: Table 5-10, Smbus interface, Functional description

Functional Description

ATCA-8330 Installation and Use (6806800S82B)

124

The nature of this security chip ensures that the information like keys, password, and digital

certificates stored within is made more secure from external software attacks and physical

theft. With the handful of keys it stores, all cryptographic functions are performed on the chip.

TPM provides the ability for a computing system to run applications more secured, allows

secured remote access, performs electronic transactions and communication more safely.

The ATCA-8330 provides an on-board Infineon SLB9635TT1.2 FW3.16 TPM Controller

connected to the LPC bus of the PCH. This advanced Infineon controller guarantees that ATCA-

8330 is fully compliant to TPM 1.2 specification.

5.19 Real Time Clock

An external 32.768 kHz clock sources the internal real time clock inside Intel DH8900CC PCH

with a frequency tolerance of 20 PPM. The RTC is fully DS1287, MC14618, PC87911, and Y2K

compliant and provides 256 bytes of backed up CMOS RAM (of which 14 bytes contain the RTC

time and date info and RTC configuration). During power-down, the RTC consumes 0.9uA/hr.

Default power-down backup solution is an external +3V lithium battery with a capacity of

200mAh, which provides 3 years of backup.

Optional power-down backup method uses a Super CAP with a 1 Farad capacity. This

provides 300 hours of RTC/SRAM backup.

5.20 SMBus

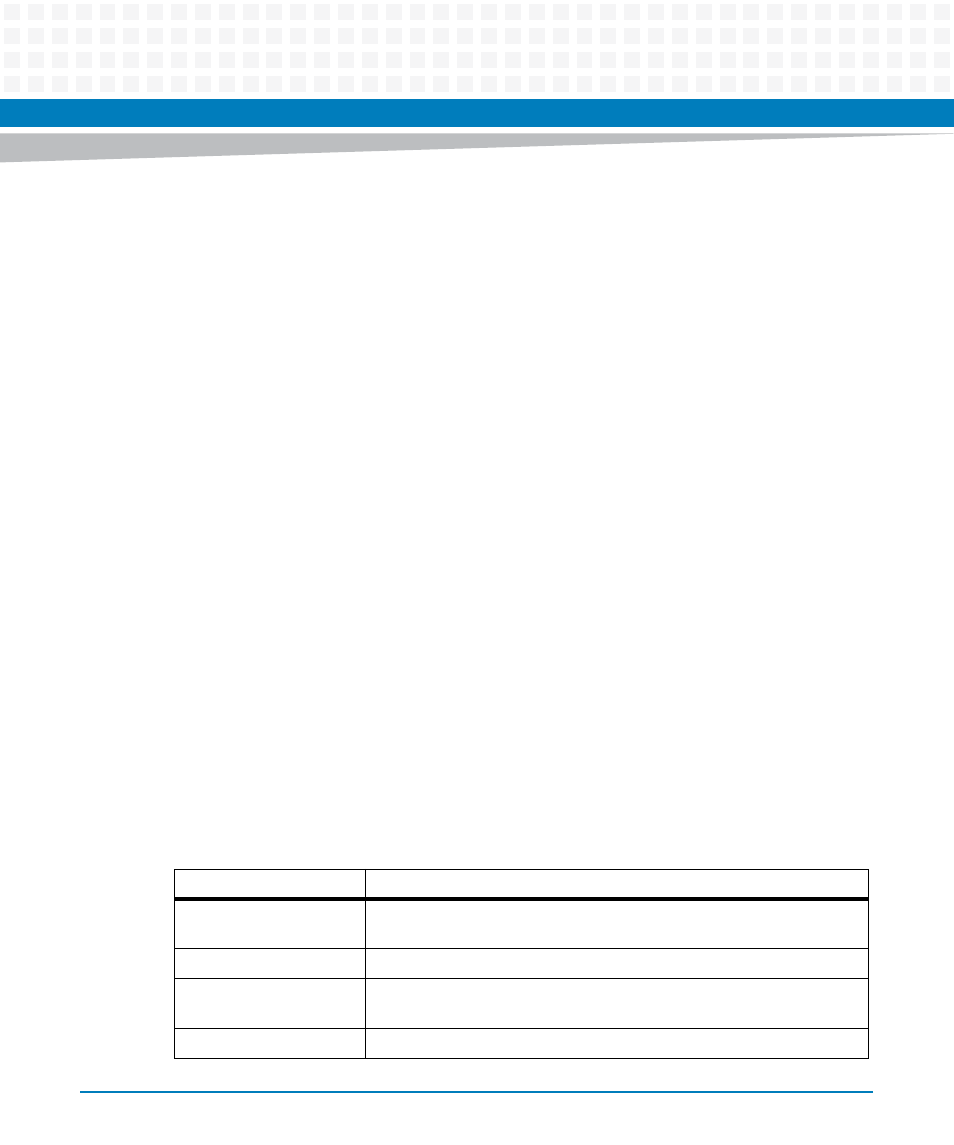

Intel DH8900CC PCH provides four SMBus interface, as described in the following table:

Table 5-10 SMBus Interface

Device / SMBus

Description

Intel DH8900CC

B0:D31:F3

Host SMBus (Master/Slave)

SMLINK1

Connection to external BMC to report thermal information

GbE SMBus

Communication between BMC and Ethernet for Passthrough Mode

(SerialOverLan) (Master/Slave)

Endpoint SMBus

Allows access to any register in PCI space of Cavecreek as PCI endpoint