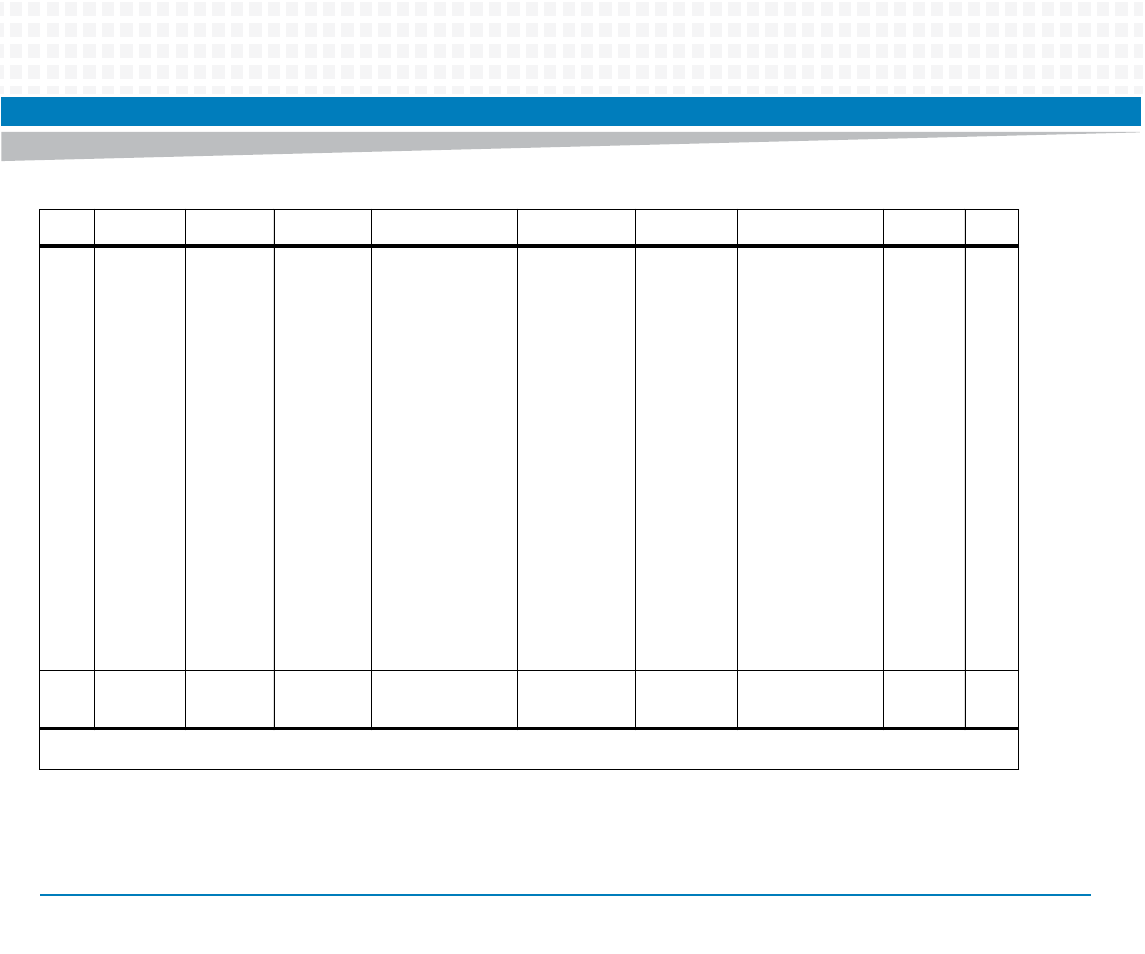

Fru information and sdr summary, Table 8-46 sensor data records (continued) – Artesyn ATCA-7368 Installation and Use (June 2014) User Manual

Page 213

FRU Information and SDR Summary

ATCA-7368 Installation and Use (6806800M12D)

213

0x27

Reset Source

OEM

0xD2

Sensor-specific

discrete

0x6F

0xA0

bit0: RST_N: Payload

Power-on reset

bit1: Reserved

bit2:

FRB_PB_RST_N:

Front board power

button reset

bit3:

PLD_PL_RST_N:

Payload Reset from

PLD (IPMC)

bit4:

RTM_PB_RST_N:

RTM power button

reset

bit5: WDG_RST_N:

FPGA internal

watchdog reset

bit6: BIOS_RST_N:

BIOS reset payload

request

bit7: OSYS_RST_N:

OS reset payload

0: Reset not

occurred

1: Reset occurred

[7:2] = Reserved

[1] = IPMC

Watchdog

Timeout

0: No IPMC

Watchdog

Timeout

1: IPMC

Watchdog

Timeout

occurred

[0] = IPMC

Watchdog Pre-

Timeout

0: No IPMC

Watchdog Pre-

Timeout

1: IPMC

Watchdog Pre-

Timeout

occurred

Payload Reset detected.

Cause delivered in Event

Byte 2 and Byte 3

Asrt

Auto

0x28

CPU Status

Processor

0x07

Sensor-specific

discrete

0x6F

[7:4] = (See IPMC Spec)

[3:0] = Offset (1)

0xFF

0xFF

0x1: Thermal Trip

Asrt

Auto

Table 8-46 Sensor Data Records (continued)

Sensor

Number Sensor Name

Sensor Type

Event/Reading

Type

Event Data Byte 1

Event Data Byte 2

Event Data Byte 3

Event

Threshold/Description

Assertion

Deassertion

Rearm

Asrt: Assertion Unr: Upper non-recoverable threshold Uc: Upper critical threshold Unc: Upper non-critical threshold

Deass: Deassertion Lnr: Lower non-recoverable threshold Lc: Lower critical threshold Lnc: Lower non-critical threshold