Altera RLDRAM II Controller MegaCore Function User Manual

Page 7

Altera Corporation

MegaCore Version 9.1

1–3

November 2009

RLDRAM II Controller MegaCore Function User Guide

About This MegaCore Function

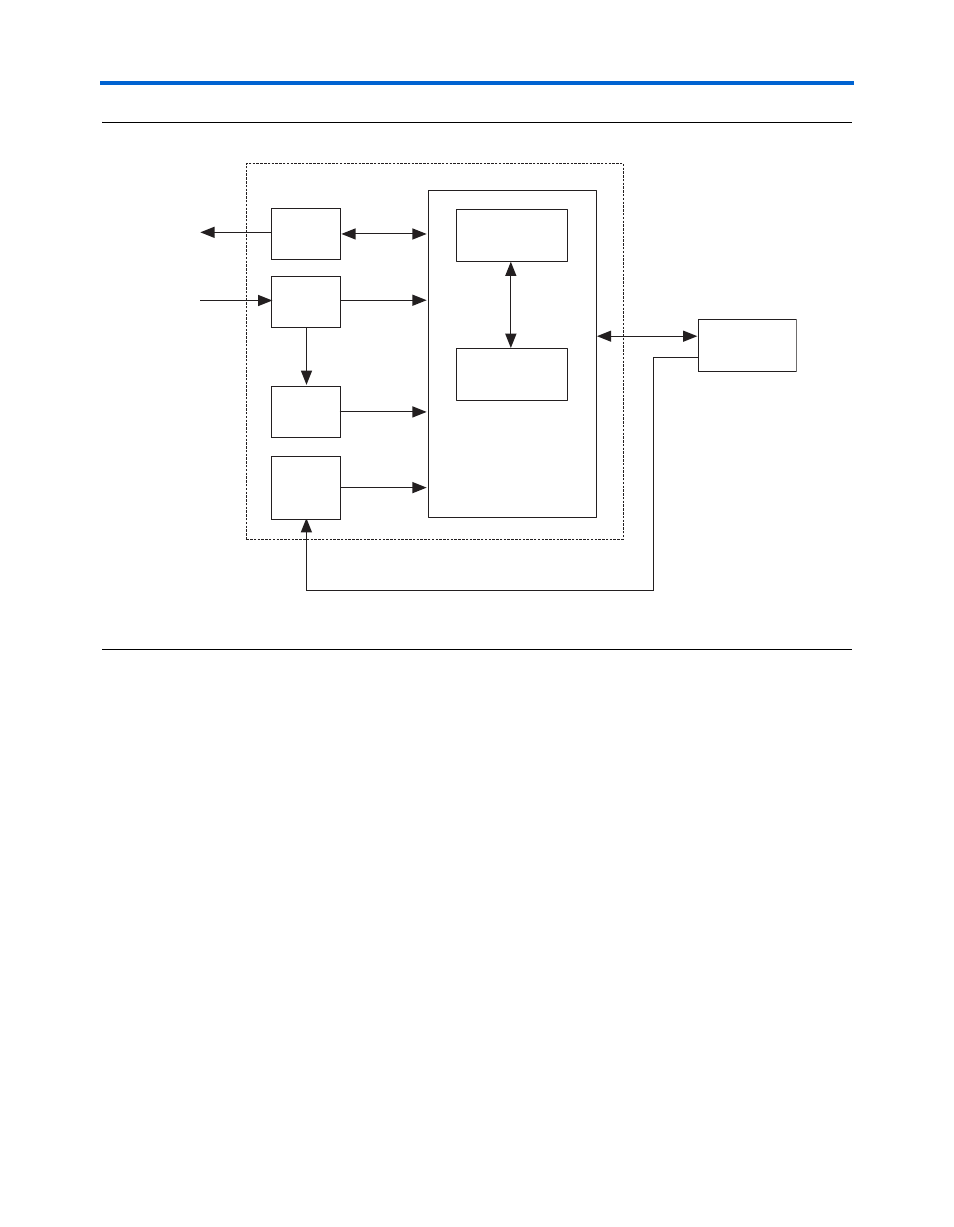

Figure 1–1. RLDRAM II Controller System-Level Diagram

Note to

:

(1)

Non-DQS mode only.

IP Toolbench generates the following items:

■

A testbench, which instantiates the example design

■

A synthesizable example design which instantiates the following

modules:

●

RLDRAM II controller:

•

Encrypted control logic, which takes transaction requests

from the local interface and issues writes, reads, and

refreshes to the memory interface

•

A clear-text datapath

●

Example driver—generates write, read and refresh requests and

outputs a pass_fail signal to indicate that the tests are

passing or failing

●

System phase-locked loop (PLL)—generates the RLDRAM II

controller clocks

●

Delay locked loop (DLL)—instantiated in DQS mode and

generates the DQS delay control signal for the dedicated DQS

delay circuitry

RLDRAM II

Example

Driver

System

PLL

DLL

RLDRAM II

Interface

Pass

or Fail

Clock

Local

Interface

Example Design

RLDRAM II Controller

Datapath

(Clear Text)

Control Logic

(Encrypted)

Fedback

Clock

PLL (

1)