Figure 2–10 – Altera RLDRAM II Controller MegaCore Function User Manual

Page 25

Altera Corporation

MegaCore Version 9.1

2–15

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

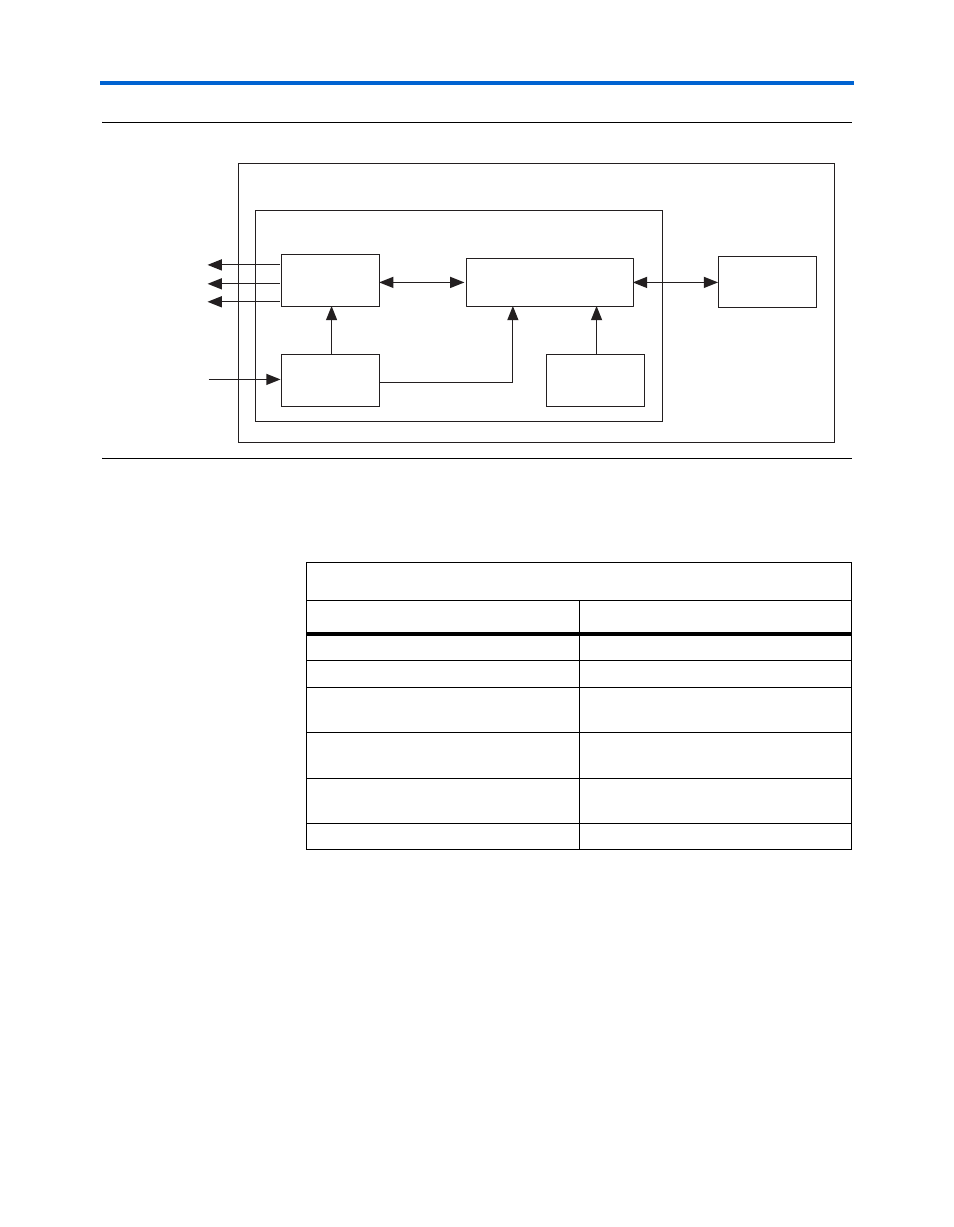

Figure 2–10. Testbench & Example Design

describes the files that are associated with the example design

and the testbench.

The testbench instantiates an RLDRAM II model and generates a

reference clock for the PLL.

1

Altera does not provide a memory simulation model. You must

download one or use your own.

Example Driver

PLL

clock_source

test_complete

pnf_persist

Example Design

Testbench

RLDRAM II Controller

RLDRAM II

Model

DLL

pnf_per_byte

Table 2–2. Example Design & Testbench Files

Filename

Description

<top-level name>_tb.v or .vhd

Testbench for the example design.

<top-level name>.vhd or .v

Example design.

rldramii_pll_

Example PLL, which you should

configure to match your frequency.

rldramii_fbpll_

.v

Fedback PLL

<variation name>_example_driver.v

or .vhd

Example driver.

RLDRAM II controller.

Notes to

:

(1)

<top-level name> is the name of the Quartus II project top-level entity.

(2)

<variation name> is the variation name.