Writes, Figure 2–11 – Altera RLDRAM II Controller MegaCore Function User Manual

Page 27

Altera Corporation

MegaCore Version 9.1

2–17

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

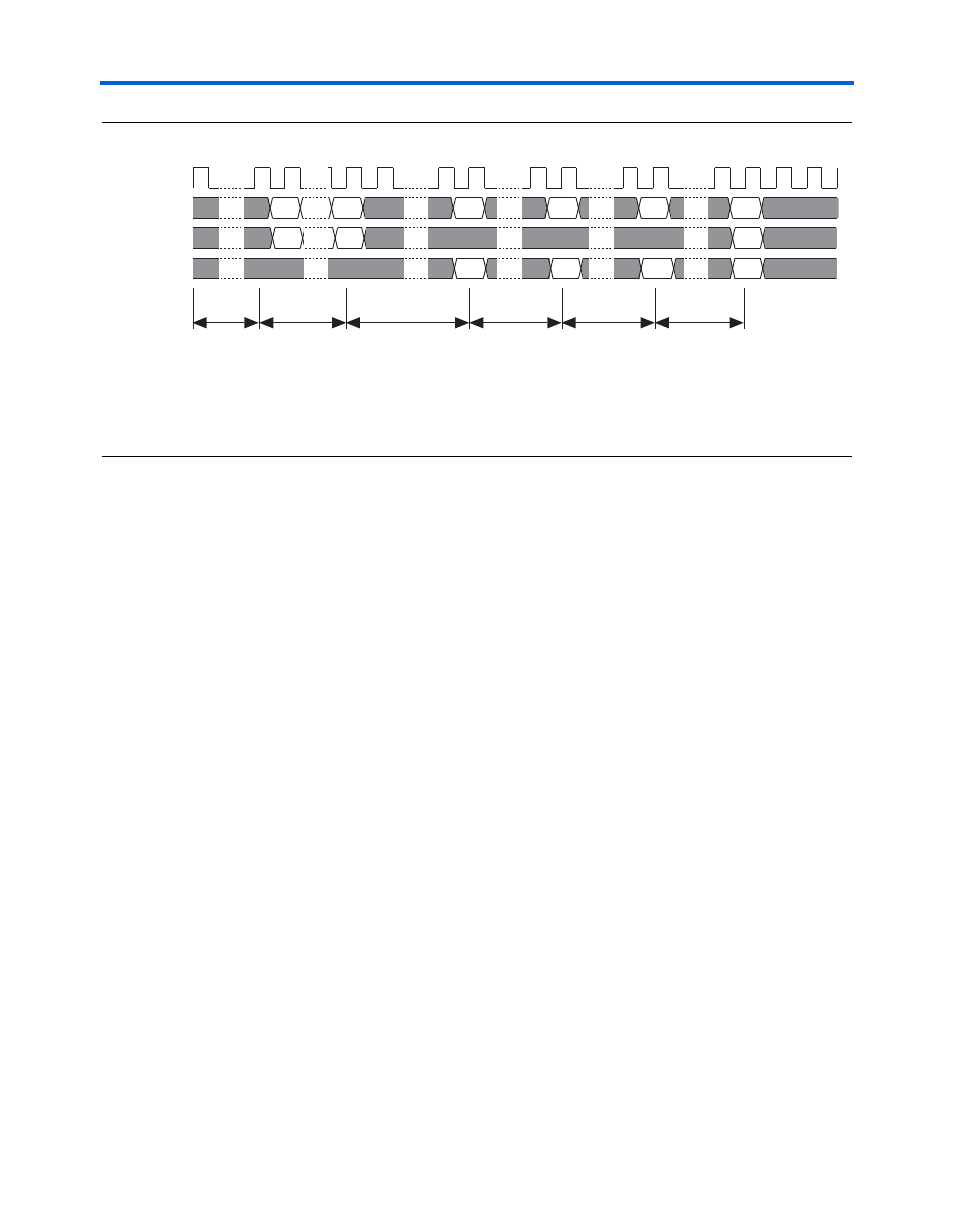

Figure 2–11. RLDRAM II Initialization Sequence

The mode register set (MRS) command configures the RLDRAM II

devices. In the ten-cycle MRS sequence, the first nine MRS commands are

dummy commands and all address bits are held at zero, to reset the

RLDRAM II DLL; the final MRS command configures the memory. The

RLDRAM II configuration data (CFG) is output on the

rldramii_a_0[]

bus during the final MRS command. The following

memory parameters are setup during the final MRS command cycle:

■

RLDRAM II termination

■

Impedance matching resistor

■

DLL enable/disable

■

RLDRAM II configuration

Writes

When you assert local_write_req, the control logic issues the write

transaction immediately at the memory interface. The control logic then

requests write data by asserting local_wdata_req, so that the

RLDRAM II t

WL

period is satisfied during write transactions. This

functionality means that the write request is decoupled from the write

data.

shows three write requests at the local and SIO RLDRAM II

interface. In this example, the memory burst length is set to eight beats.

The RLDRAM II device is setup with a t

RC

of six-clock cycles

(configuration two).

rldramii_cl k

Command

MRS = Mode Register Set

CFG = Mode Register Configuration Data

RFx = Refresh

AC = User Command

rldramii_a[ ]

rldramii_ba[

2,048

Clock Cycles

t

MRSC

t

RC

6 x 2,048

Clock Cycles

10 Clock

Cycles

200

ms

Minimum

]

MRS

MRS

RF0

RF1

RF7

AC

AC

0

0

CFG

Ax

Ax

0

1

7

Bx

Bx