Of six-clock cycles (configuration two) – Altera RLDRAM II Controller MegaCore Function User Manual

Page 28

2–18

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

Interfaces

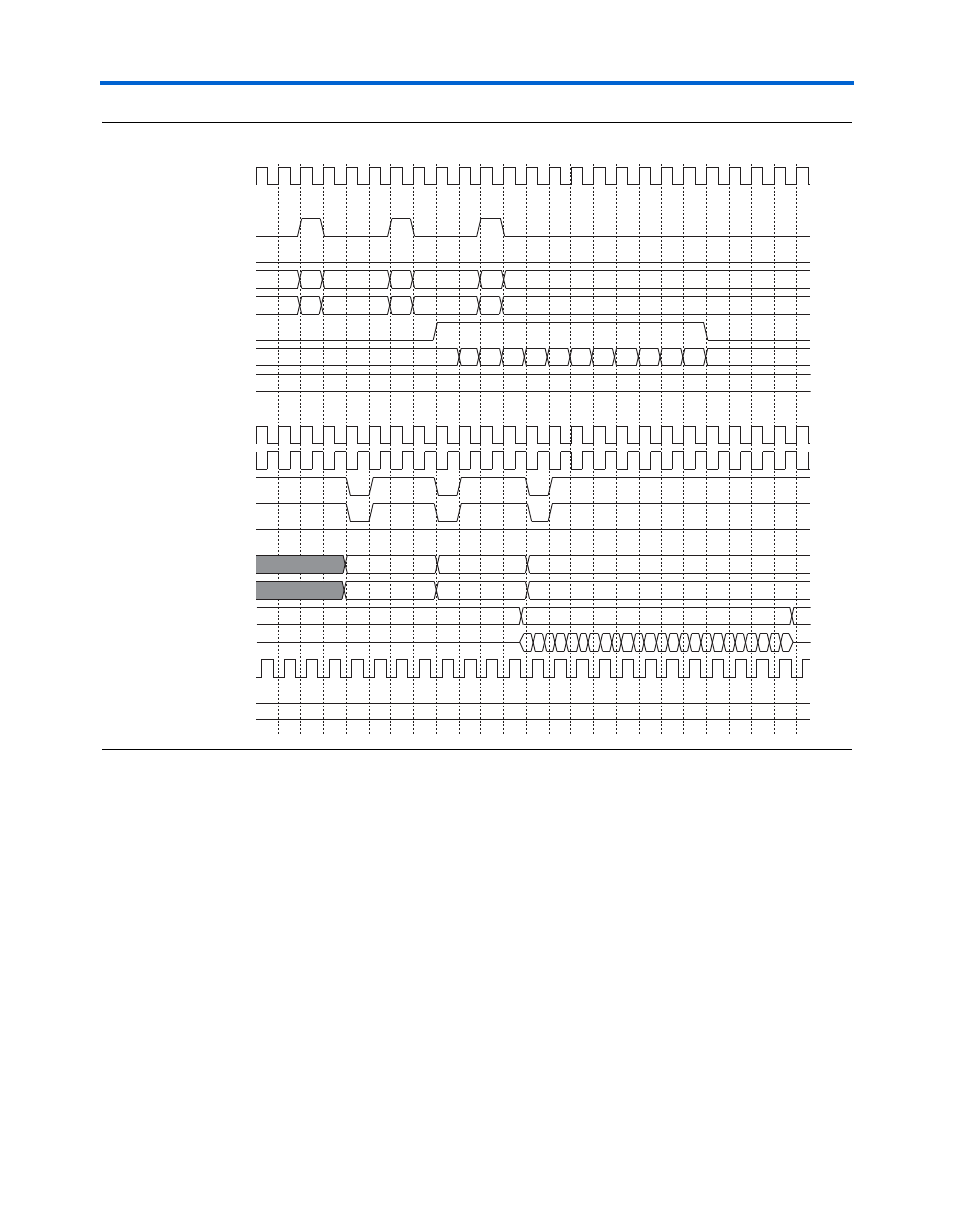

Figure 2–12. Write Example

shows the transactions at the local interface are separated by

the correct number of clock cycles for the target RLDRAM II device

configuration. If transaction requests are supplied to the RLDRAM II

controller with the incorrect spacing the controller executes these

transactions as requested, which can result in incorrect behavior.

shows an example of a write following a read at a CIO

RLDRAM II interface. In this example, the memory burst length is set to

two beats. The RLDRAM II device is setup with a t

RC

of six-clock cycles

(configuration two).

f

For more information about bus turnaround timing calculations with

CIO devices, refer to AN 325: Interfacing RLDRAM II with Stratix II,

Stratix & Stratix GX Devices.

clk

Local Interface

local_write_req

local_read_req

local_addr[]

local_ba[]

local_wdata_req

local_wdata[]

local_dm[]

RLDRAM II Interface

rldramii_clk

rldramii_clk_n

rldramii_cs_n

rldramii_we_n

rldramii_ref_n

rldramii_a[]

rldramii_ba[]

A

B

C

C

A

B

C

C

A01 A23A45 A67 B01 B23 B45 B67 C01 C23 C45

C67

00

A

B

C

B

A

B

C

B

rldramii_d[]

rldramii_qk[]

rldramii_qvld[]

rldramii_q[]

0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7

7

rldramii_dm[]

11

11

00