Memory – Altera RLDRAM II Controller MegaCore Function User Manual

Page 39

Altera Corporation

MegaCore Version 9.1

2–29

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

Memory

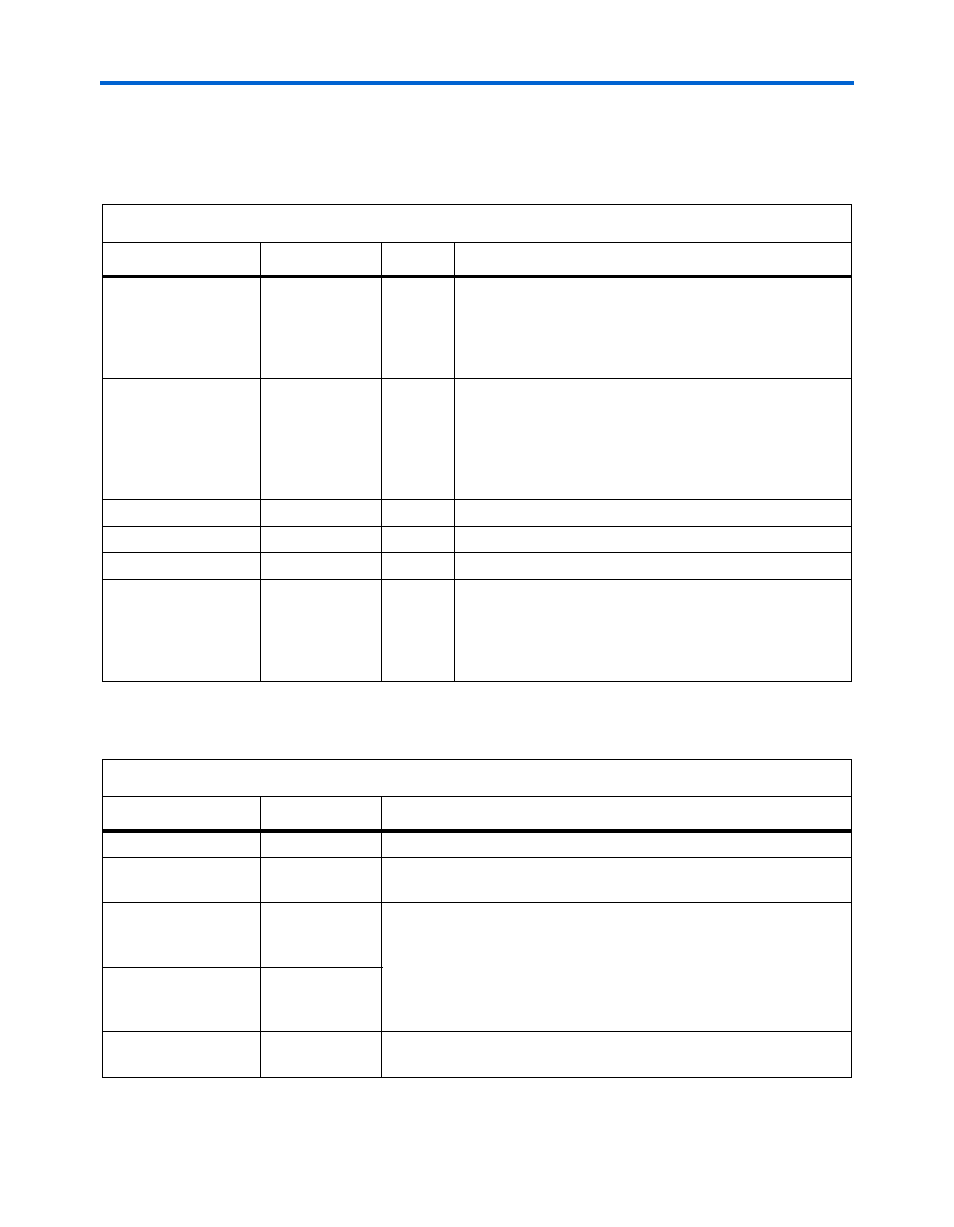

shows the memory type parameters.

shows the memory initialization options.

Table 2–7. Memory Type Parameters

Parameter

Range

Units

Description

RLDRAM II device

Part number

–

A part number for a particular memory device. Choosing

an entry sets many of the parameters in the wizard to the

correct value for the specified part. You can add your own

devices to this list by editing the memory_types.dat file in

the \constraints directory.

Clock speed

100 to 400

MHz

The memory controller clock frequency.The constraints

script and the datapath use this clock speed. It must be set

to the value that you intend to use. The first time you use

IP Toolbench or if you turn on Update example design

system PLL, it uses this value for the IP Toolbench-

generated PLL’s input and output clocks.

Interface voltage

1.5 or 1.8

V

The RLDRAM II interface voltage.

DQ per DQS

8, 9, 16, 18

Bits

Number of DQ bits per DQS input pin. CIO devices only.

Q per DQS

8, 9, 16, 18

Bits

Number of Q bits per DQS input pin. SIO devices only.

Data-bus width

Device

dependent

Bits

The width of the memory interface.

For more information about supported interface data

widths, refer to AN 325: Interfacing RLDRAM II with Stratix

II, Stratix & Stratix GX Devices.

Table 2–8. Memory Initialization Options

Parameter

Range

Description

Memory configuration 1, 2, or 3.

Refer to your RLDRAM II data sheet.

Burst length

2, 4, or 8

Number of beats in the burst at the memory interface. The number of

beats at the local interface is half this value.

Manually enter

initialization clock

cycles

On or off

The wizard takes the number of initialization clock cycles from the

memory.dat file in the constraints directory. The number is

calculated from the initialization entry time and the clock speed. You

can manually enter a number for the initialization clock cycles if you

turn on Manually enter initialization clock cycles.

Number of

initialization clock

cycles

16 to 80,000

Enable on-die

termination

On or off

Refer to your RLDRAM II data sheet.