Altera RLDRAM II Controller MegaCore Function User Manual

Page 34

2–24

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

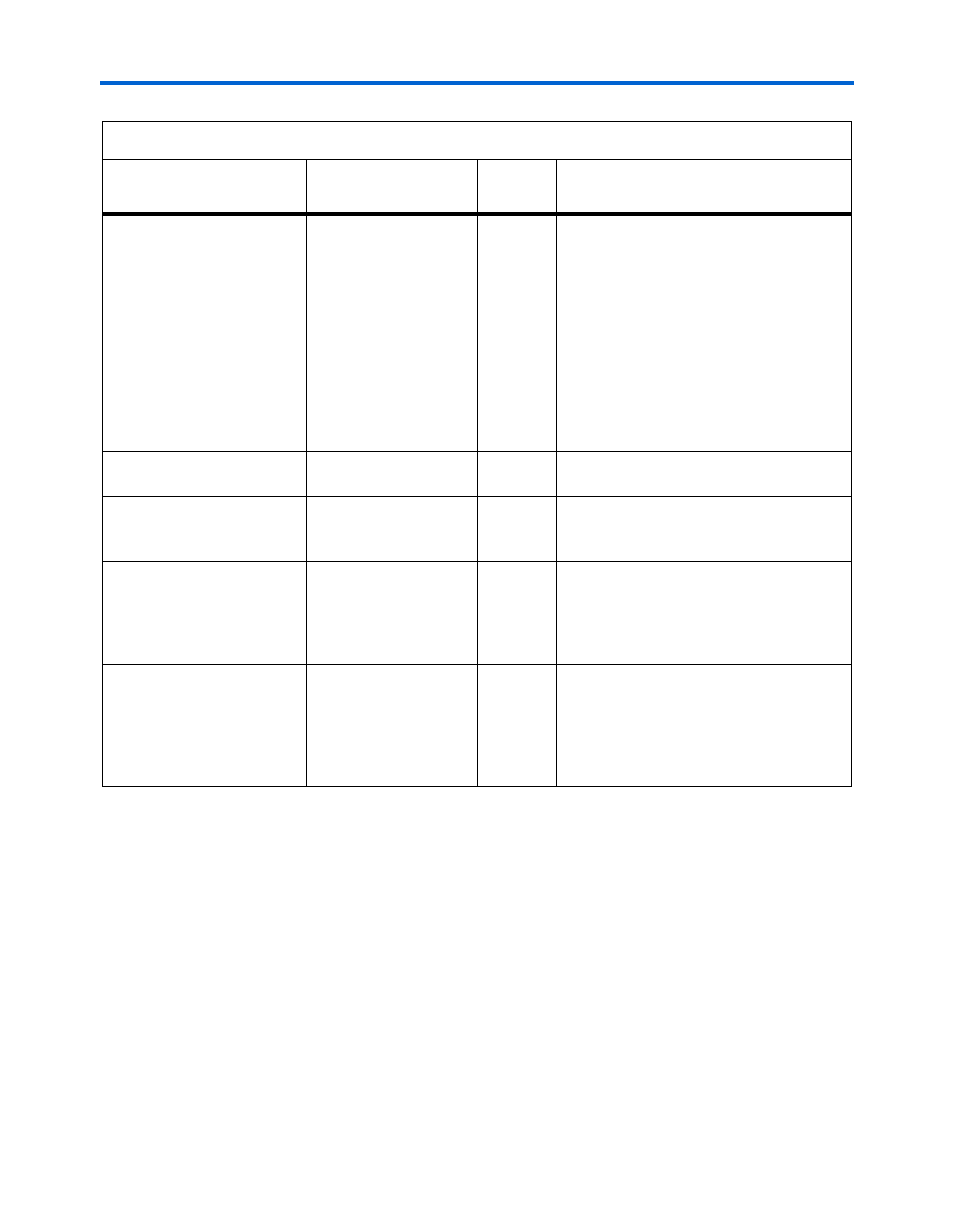

Signals

addr_cmd_clk

1

Input

Address and command output register

clock. The

addr_cmd_clk

clock

frequency must be the same as the system

clock,

clk

, and the write clock,

write_clk

, frequencies.

In addition, when there is a separate

address and command clock phase, no

timing paths related to this clock should be

cut, to ensure that any paths using a

separate clock for address and command

are timing analysed.

dqs_delay_ctrl[]

6

Input

Delay bus for DLL to shift DQS inputs. DQS

mode only.

non_dqs_capture_clk

1

Input

Optional clock that captures read data and

clocks read data logic. Non-DQS mode

only.

reset_clk_n

1

Input

Reset input for logic on the system clock

domain. The

reset_clk_n

can be

asserted asynchronously but must be

deasserted synchronous to the rising edge

of the system clock.

reset_addr_cmd_clk_n

1

Input

Reset input for logic on the address and

command clock domain. The

reset_addr_cmd_clk_n

can be

asserted asynchronously but must be

deasserted synchronous to the rising edge

of the address and command clock.

Table 2–3. System Signals (Part 2 of 3)

Name

Width

(Bits)

Direction

Description