Project settings – Altera RLDRAM II Controller MegaCore Function User Manual

Page 42

2–32

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

Parameters

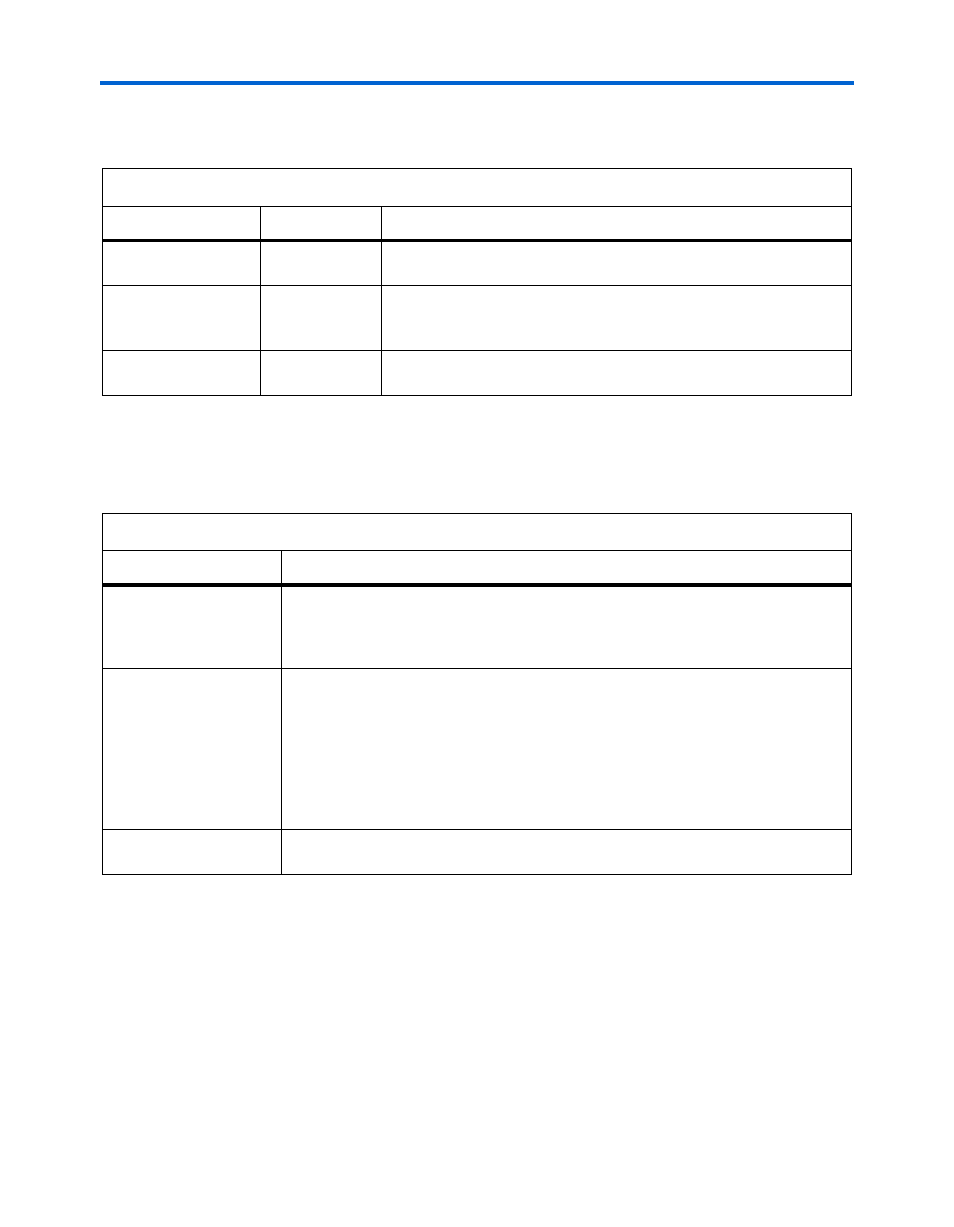

shows the pin loading parameters.

Project Settings

shows the example design settings.

Table 2–12. Pin Loading Parameters

Parameter

Range (pF)

Description

Pin loading on FPGA

DQ/DQS pins

0 to 100

Enter the pin loading to match your board and memory devices.

Pin loading on FPGA

address and

command pins

0 to 100

Enter the pin loading to match your board and memory devices.

Pin loading on FPGA

clock pins

0 to 100

Enter the pin loading to match your board and memory devices.

Table 2–13. Example Design Settings

Parameter

Description

Automatically apply

RLDRAM II controller-

specific constraints to the

Quartus II project

When this option is turned on, the next time you compile, the Quartus II software

automatically runs the add constraints script. Turn off this option if you do not want

the script to run automatically.

Update the example

design file that

instantiates the RLDRAM

II controller variation

When this option is turned on, IP Toolbench parses and updates the example design

file. It only updates sections that are between the following markers:

<

<

If you edit the example design file, ensure that your changes are outside of the

markers or remove the markers. Once you remove the markers, you must keep the

file updated, because IP Toolbench can no longer update the file.

Update example design

system PLL

When this option is turned on, IP Toolbench automatically overwrites the PLL.Turn off

this option, if you do not want the wizard to overwrite the PLL.