Table 2–5 – Altera RLDRAM II Controller MegaCore Function User Manual

Page 36

2–26

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

Signals

shows the memory interface signals.

local_wdata[]

Data-bus width × 2

Input

Write data bus. The local interface must request

local_wdata[]

over multiple clock cycles to

construct the write data for any requested write

bursts. If the memory burst length is set to two

beats, the write data is requested in a single

clock cycle at the local interface.

local_write_req

1

Input

Write request signal.

local_init_done

1

Output

Memory initialization complete signal which is

asserted when the controller has completed its

initialization of the memory. Reads and writes

should not be requested until

local_init_done

is asserted.

local_rdata[]

Data-bus width × 2

Output

Read data bus. The controller returns

local_rdata[]

over multiple clock cycles for

any requested read transactions. If the memory

burst length is set to two beats, the read data is

returned in a single clock cycle at the local

interface.

local_rdata_valid

[]

The number of

RLDRAM II devices

attached to memory

interface

Output

Read data valid signal, which indicates that valid

data is present on the read data bus. The

local_rdata_valid[]

signal is aligned with

the local read data,

local_rdata[]

. There is

only one

local_rdata_valid[]

per

attached RLDRAM II device.

local_wdata_req

1

Output

Write data request signal. When the local

interface asserts

local_wdata_req

, all the

write data for the burst should be available in

contiguous clock cycles.

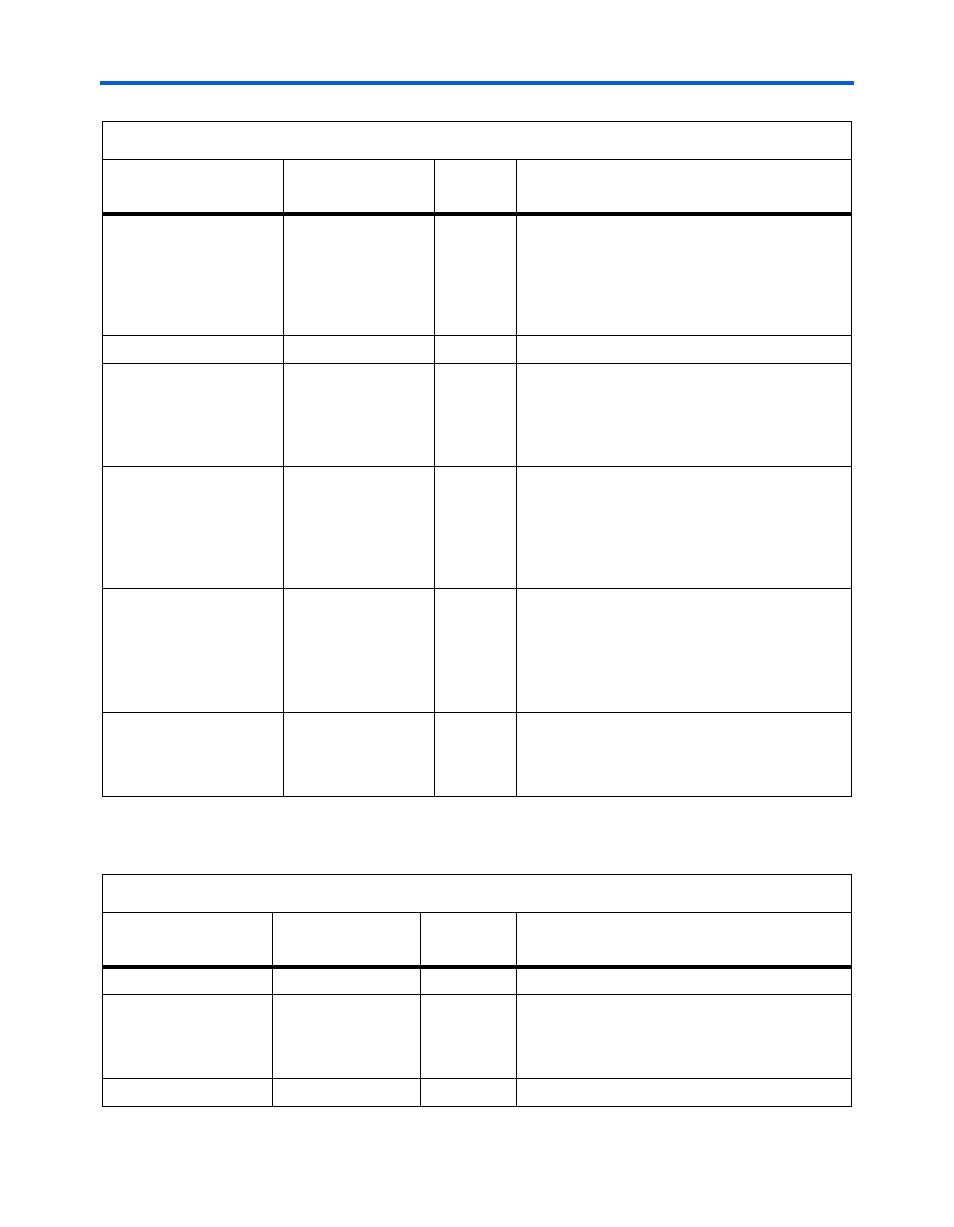

Table 2–4. Local Interface Signals (Part 2 of 2)

Name

Width

(Bits)

Direction

Description

Table 2–5. Memory Interface Signals (Part 1 of 2)

Name

Width

(Bits)

Direction

Description

rldramii_dq[]

Data-bus width

Bidirectional

Memory data bus. CIO devices only.

rldramii_qk[]

1 to 9

Bidirectional

In DQS mode, the memory data strobe signal

that captures read data into the Altera device; in

non-DQS mode, the RLDRAM II controller does

not use

rldramii_qk[]

.

rldramii_q[]

Data-bus width

Input

Memory read data bus. SIO devices only.