Altera RLDRAM II Controller MegaCore Function User Manual

Page 37

Altera Corporation

MegaCore Version 9.1

2–27

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

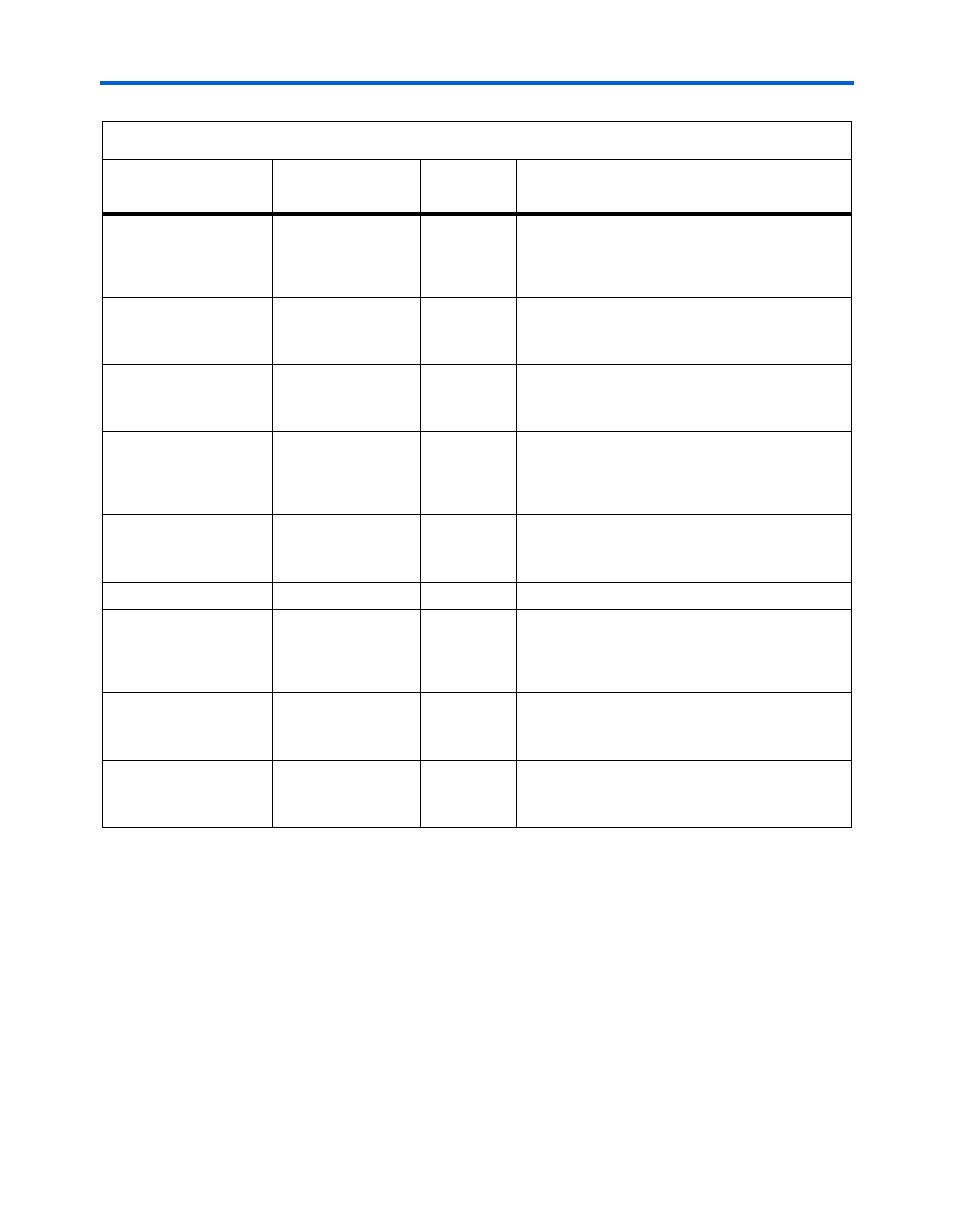

rldramii_qvld[]

The number of

RLDRAM II devices

attached to memory

interface

Input

Read data valid flag.

rldramii_a_0[]

rldramii_a_1[]

local_addr[]

Output

Memory address signals.

rldramii_ba_0[]

rldramii_ba_1[]

3

Output

Memory bank address signals.

rldramii_clk[],

rldramii_clk_n[]

1 to 3 (wtih

dedicated PLL

clocks) or 1 to 8

otherwise

Output

Memory command output clock.

rldramii_cs_n_0

rldramii_cs_n_1

1

Output

Memory chip select signal.

rldramii_d[]

Data-bus width

Output

Memory write data bus. SIO devices only.

rldramii_dm[]

The number of

RLDRAM II devices

attached to memory

interface

Output

Memory DM (optional).

rldramii_ref_n_0

rldramii_ref_n_1

1

Output

Memory refresh request signal.

rldramii_we_n_0

rldramii_we_n_1

1

Output

Memory write enable signal.

Note to

:

(1)

The default signal is <signal>_0. When you specify additional address and command busses, both <signal>_0 and

<signal>_1 are present.

Table 2–5. Memory Interface Signals (Part 2 of 2)

Name

Width

(Bits)

Direction

Description