Altera RLDRAM II Controller MegaCore Function User Manual

Page 40

2–30

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

Parameters

shows the memory interface parameters.

Enable external

impedance matching

On or off

Refer to your RLDRAM II data sheet.

Enable memory

device DLL

On or off

Refer to your RLDRAM II data sheet.

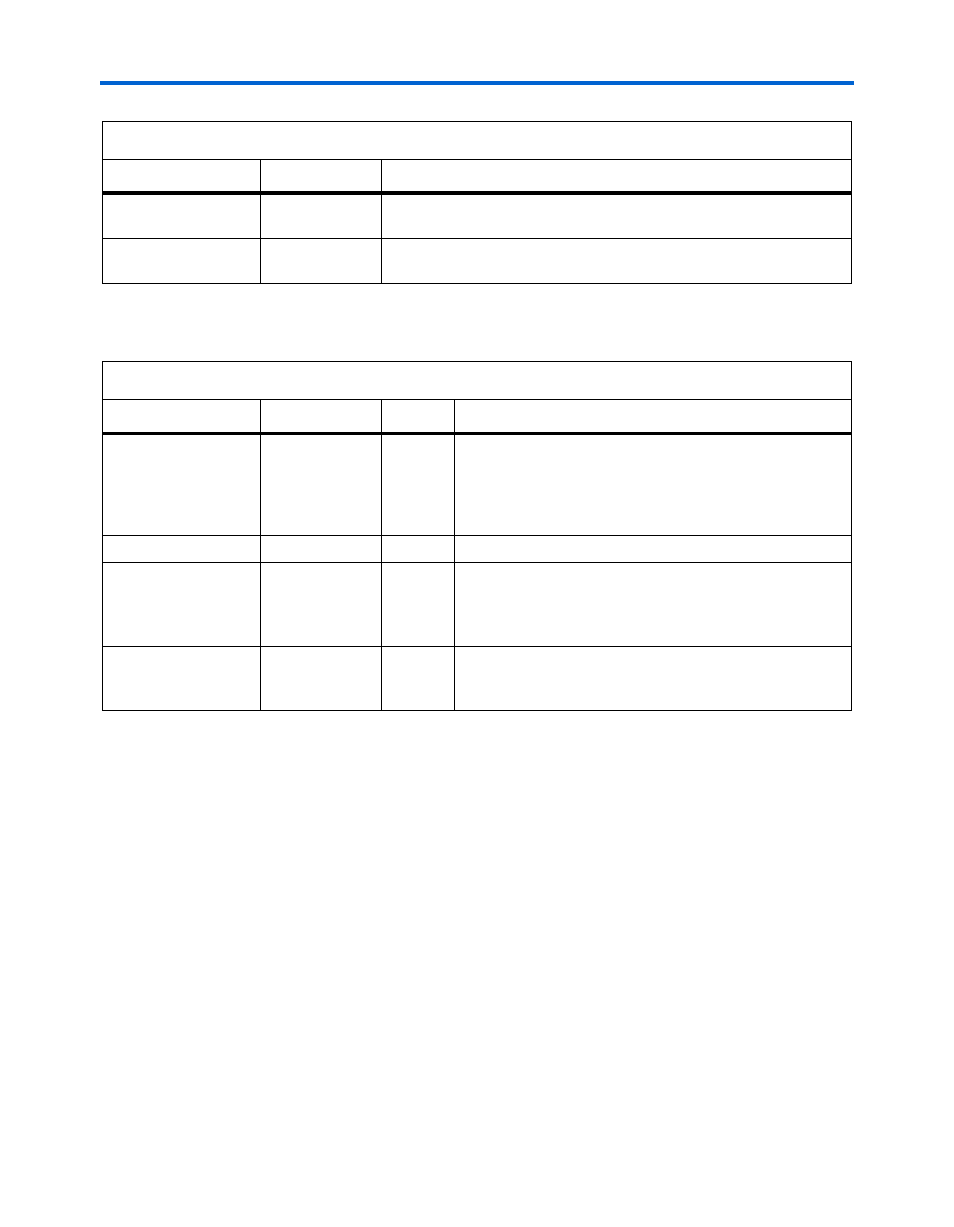

Table 2–8. Memory Initialization Options

Parameter

Range

Description

Table 2–9. Memory Interface Parameters

Parameter

Range

Units

Description

Number of address

and command busses

from FPGA to

memory for multiple

devices

1 or 2

–

Depends on the number of devices. If you connect only

one device there can be only one address and command

bus.

Generate DM pins

On or off

–

Adds DM pins and logic to the design.

Use dedicated PLL

outputs

On or off

–

Turn on to use dedicated PLL outputs to generate the

clocks, which is recommended for HardCopy II devices.

When turned off

altddio

outputs generate the clock

outputs.

Number of clock pairs

from FPGA to

memory

1 to 8

–

The number of RLDRAM II clock output pairs generated in

the datapath. When you turn on Use dedicated clock

outputs, only values of 1 to 3 are valid.

Note to

:

(1)

The default signal is <signal>_0. When you specify additional address and command busses, both <signal>_0 and

<signal>_1 are present.