Parameters, Parameters –28 – Altera RLDRAM II Controller MegaCore Function User Manual

Page 38

2–28

MegaCore Version 9.1

Altera Corporation

RLDRAM II Controller MegaCore Function User Guide

November 2009

Parameters

shows the datapath interface signals.

Parameters

The parameters can only be set in IP Toolbench (see

).

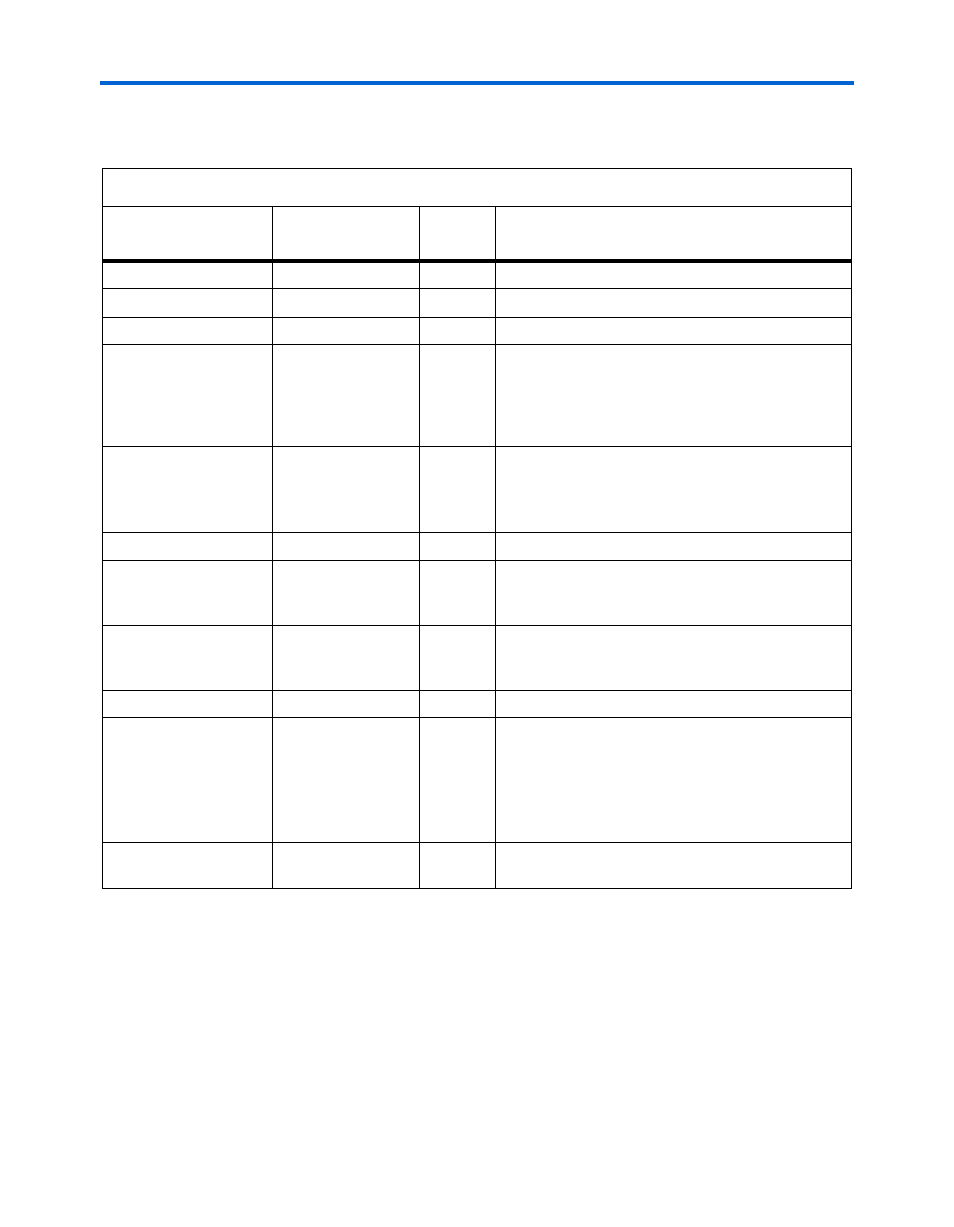

Table 2–6. Datapath Interface Signals

Name

Width

(Bits)

Direction

Description

control_a[]

local_addr[]

Input

Address bits.

control_ba[]

3

Input

Bank address bits.

control_cs_n

1

Input

Chip select signal.

control_dm[]

The number of

RLDRAM II devices

attached to the

memory interface ×

2

Input

The DM bus, which has valid data in the same clock

cycles that

control_wdata_valid

is asserted.

control_doing_wr

1

Input

Control_doing_wr

is asserted when the

controller is writing to the RLDRAM II devices and

controls the output enables on

rldramii_dq[]

or

rldramii_d[]

.

control_ref_n

1

Input

Refresh signal.

control_wdata[]

Data-bus width × 2

Input

The write data bus, which has valid data in the same

clock cycles that

control_wdata_valid

is

asserted.

control_wdata_

valid

1

Input

Enables the write data bus and DM enable registers

so that they are only updated when valid data and

enables are available.

control_we_n

1

Input

Write enable signal.

control_qvld[]

The number of

RLDRAM II devices

attached to the

memory interface

Output

The read data valid flag.There is only one QVLD flag

per RLDRAM II device. The

control_qvld[]

signal is aligned with the valid

control_rdata[]

and is asserted during this period. The

control_qvld[]

signal has the same

functionality as

local_rdata_valid[]

.

control_rdata[]

Data-bus width × 2

Output

The captured read data (same as

local_rdata[]

).