Megacore verification, Simulation environment, Hardware testing – Altera RLDRAM II Controller MegaCore Function User Manual

Page 43: Megacore verification –33

Altera Corporation

MegaCore Version 9.1

2–33

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

shows the variation path parameters.

shows the device pin prefixes parameter.

MegaCore

Verification

MegaCore verification involves simulation testing and hardware testing.

Simulation Environment

Altera has carried out extensive functional tests using industry-standard

models to ensure the functionality of the RLDRAM II controller. In

addition, Altera has carried out a wide variety of gate-level tests on the

RLDRAM II controller to verify the post-compilation functionality of the

controller.

Hardware Testing

shows the Altera development board on which Altera

hardware tested the RLDRAM II controller.

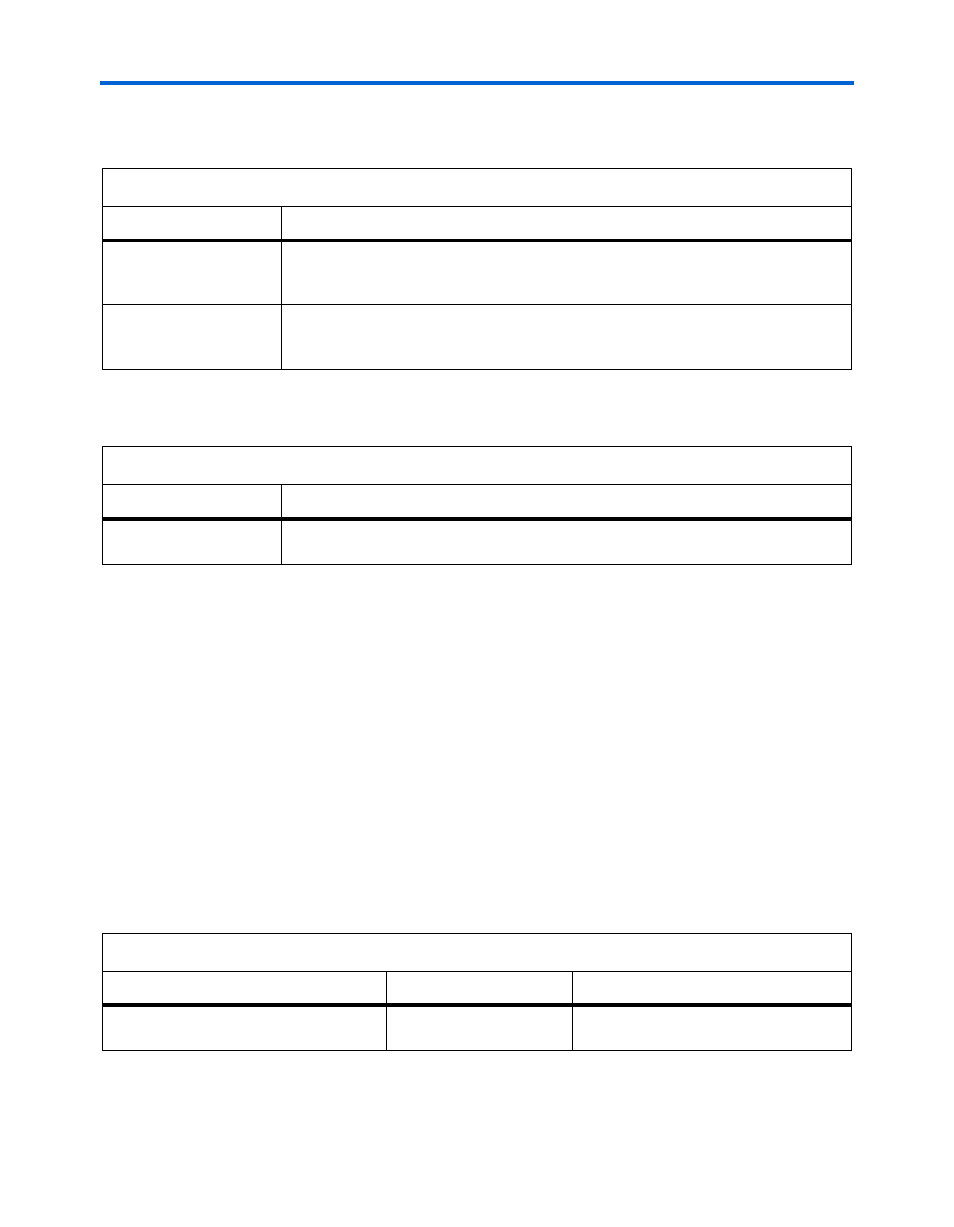

Table 2–14. Variation Path Parameters

Parameter

Description

Enable hierarchy control

The constraints script analyzes your design, to automatically extract the hierarchy to

your variation. To prevent the constraints script analyzing your design, turn on

Enable Hierarchy Control, and enter the correct hierarchy path to your datapath.

Hierarchy path to

RLDRAM II controller

datapath

The hierarchy path is the path to your RLDRAM II controller datapath, minus the top-

level name. The hierarchy entered in the wizard must match your design, because

the constraints scripts rely on this path for correct operation.

Table 2–15. Device Pin Prefixes

Parameter

Description

Prefix all RLDRAM II pins

on the device with

This string prefixes the pin names for the FPGA pins that are connected to the

RLDRAM II controller.

Table 2–16. Altera Development Boards

Development Board

Altera Device

Memory Device

Stratix II Memory Demonstration Board 1 EP2S60F1020C3

Micron 18-bit CIO and SIO RLDRAM II

devices