Timing – Altera RLDRAM II Controller MegaCore Function User Manual

Page 41

Altera Corporation

MegaCore Version 9.1

2–31

November 2009

RLDRAM II Controller MegaCore Function User Guide

Functional Description

Timing

shows the pipeline options.

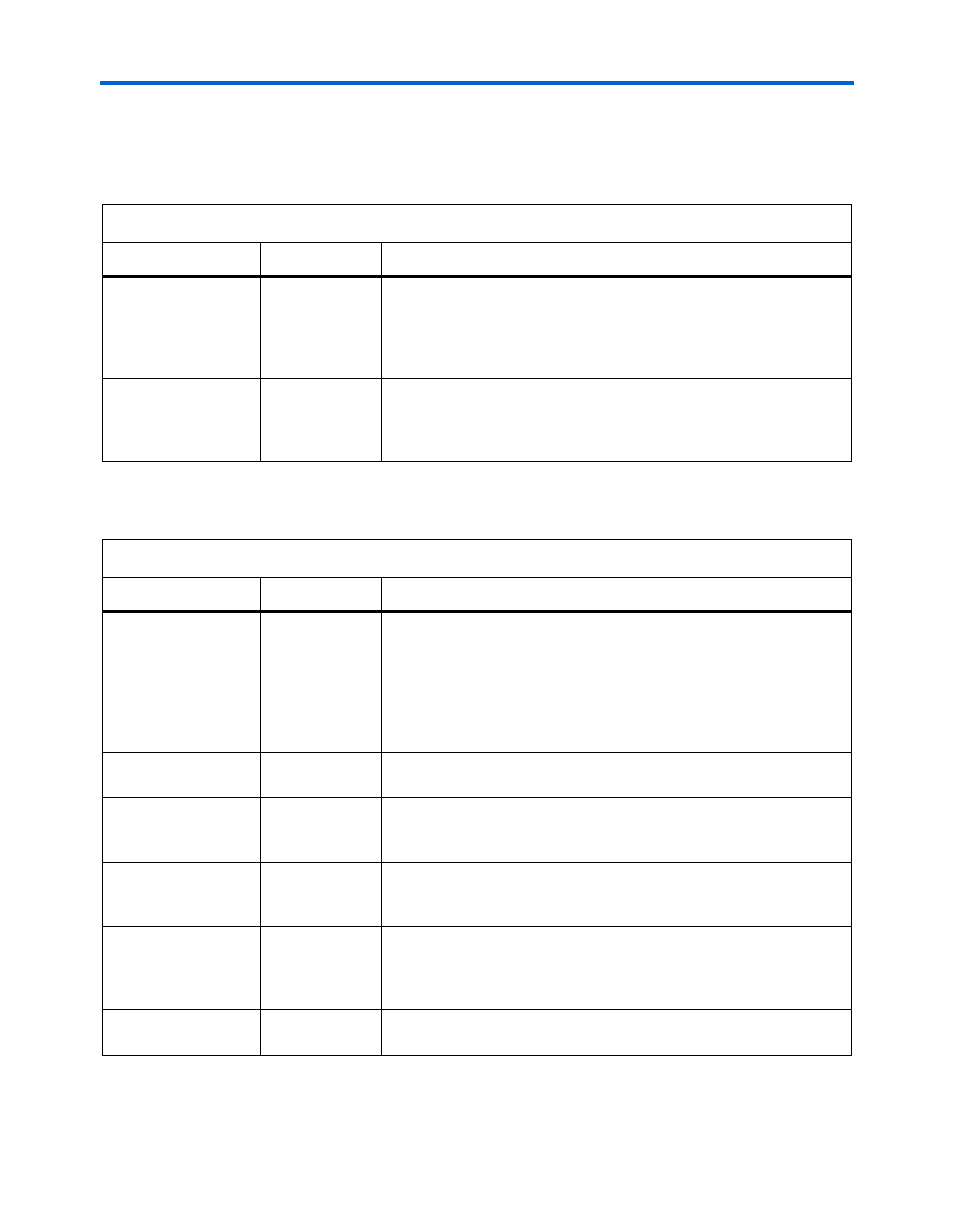

Table 2–10. Pipeline Options

Parameter

Range

Description

Number of address

and command and

write data pipeline

registers

0, 1, 2 or 3

When you choose 1, 2, or 3 the wizard inserts 1, 2, or 3 pipeline

registers between the memory controller and the command and

address output registers and the write data output registers. These

registers may help to achieve the required performance at higher

frequencies.

Number of read data

pipeline registers

0, 1, 2 or 3

When you choose 1, 2, or 3 the wizard inserts 1, 2, or 3 pipeline

registers between the read capture registers and the memory

controller. These registers may help to achieve the required

performance at higher frequencies.

Table 2–11. Clocking Modes

Parameter

Range

Description

Address and

command clock

System, write,

or dedicated

The clock for the address and command output registers. For

system_clk

choose System; for

write_clk

, choose Write, and

for a separate clock, choose Dedicated.

If you choose Dedicated for the clock, ensure the clock phase allows

the Quartus II software to meet the setup time on the address and

command output registers.

Address and

command clock edge

Falling or rising

The clock edge on which the addresses and commands are output.

Dedicated address

and command clock

PLL phase offset

± 180

Sets the dedicated address and command clock PLL phase for better

timing.

Enable DQS mode

On or off

Turn on for DQS mode; otherwise the controller is in non-DQS mode

(Stratix II and Stratix II GX devices only). HardCopy II devices allow

DQS mode only.

Use migratable byte

groups

On or off

When turned on, you can migrate the design to a migration device.

When turned off the wizard allows much greater flexibility in the

placement of byte groups. You can only turn on this option when

Enable DQS mode is turned off.

Fedback PLL phase

offset

± 180

Sets the fedback clock PLL phase for read capture (non-DQS mode

only).