NEC PD754144 User Manual

Page 99

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

99

User’s Manual U10676EJ3V0UM

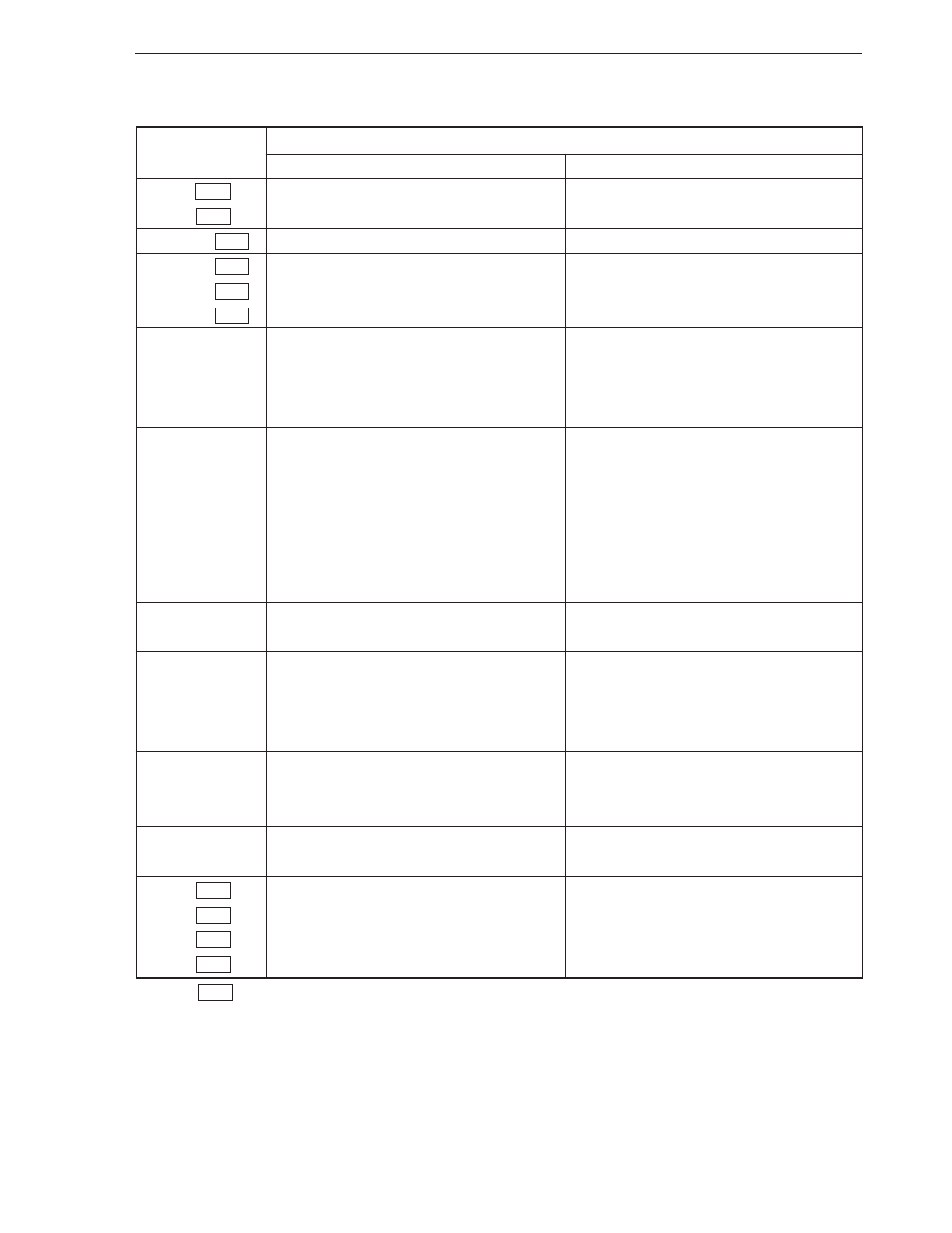

Table 6-3. Operation When I/O Port Is Manipulated

Operation of Port and Pin

Input mode

Output mode

SKT

<1>

Tests pin data

Tests output latch data

SKF

<1>

MOV1 CY, <1>

Transfers pin data to CY

Transfers output latch data to CY

AND1

CY, <1>

Performs operation between pin data and CY

Performs operation between output latch data

OR1

CY, <1>

and CY

XOR1

CY, <1>

IN

A, PORTn

Transfers pin data to accumulator

Transfers output latch data to accumulator

MOV

A, PORTn

MOV

A, @HL

MOV

XA, @HL

ADDS

A, @HL

Performs operation between pin data and

Performs operation between output latch data

ADDC A, @HL

accumulator

and accumulator

SUBS

A, @HL

SUBC

A, @HL

AND

A, @HL

OR

A, @HL

XOR

A, @HL

SKE

A, @HL

Compares pin data with accumulator

Compares output latch data with accumulator

SKE

XA, @HL

OUT

PORTn, A

Transfers accumulator data to output latch

Transfers accumulator data to output latch and

MOV

PORTn, A

(output buffer remains off)

outputs data from pins

MOV

@HL, A

MOV

@HL, XA

XCH

A, PORTn

Transfers pin data to accumulator and accumulator

Exchanges data between output latch and

XCH

A, @HL

data to output latch (output buffer remains off)

accumulator

XCH

XA, @HL

INCS

PORT

Increments pin data by 1 and latches it to output

Increments output latch contents by 1

INCS

@HL

latch

SET1

<1>

Rewrites output latch contents of specified bit as

Changes status of output pin as specified by

CLR1

<1>

specified by instruction. However, output latch

instruction

MOV1

<1> , CY

contents of other bits are undefined

SKTCLR <1>

Remark

<1> : Indicates two addressing modes: PORTn, bit and PORTn.@L.

Instruction Executed