NEC PD754144 User Manual

Page 169

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

169

User’s Manual U10676EJ3V0UM

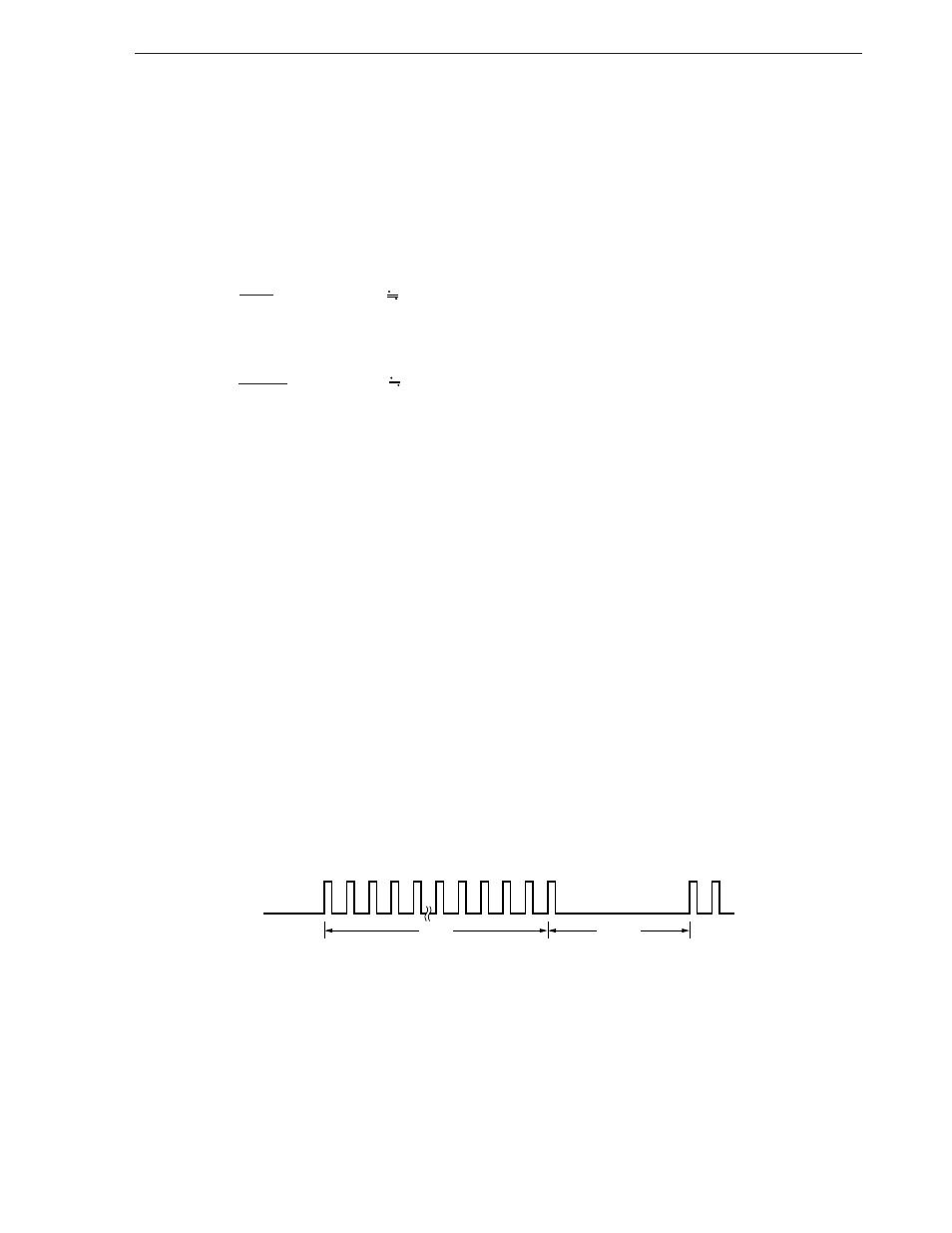

<2> To output a leader code with a 9 ms period to output a carrier clock and a 4.5 ms period to output a

low level (Refer to the figure below.)

•

Set the higher 4 bits of the timer counter mode register (TM1) to 0110B and select 15.6 ms as the

longest set time.

•

Set the lower 4 bits of TM1 to 1100B. Then, select the 8-bit timer counter mode, count operation,

and timer start command.

•

The initial set value of the timer counter modulo register (TMOD1) is as follows.

– 1 = 147.5 – 1

147 = 93H

•

The set value for rewriting TMOD1 is as follows.

– 1 = 73.8 – 1

73 = 49H

•

Set the higher 4 bits of TC2 to 0000B.

•

Set the lower 4 bits of TC2 to 0000B. The carrier clock is output when no return zero data is “1”,

and the no return zero data to be output next is cleared to “0”.

SEL

MB15

;

or CLR1 MBE

MOV

XA, #093H

MOV

TMOD1, XA

;

Sets modulo (carrier clock output period)

MOV

XA, #00000000B

MOV

TC2, XA

SET1

NRZ

;

Sets no return zero data to “1”

MOV

XA, #01101100B

MOV

TM1, XA

;

Sets mode and starts timer

EI

;

Enables interrupt

EI

IET1

;

Enables interrupt of timer counter channel 1

;

MOV

XA, #049H

MOV

TMOD1, XA

;

Rewrites modulo (low-level output period)

RETI

9 ms

4.5 ms

4.5 ms

61

µs

9 ms

61

µs