NEC PD754144 User Manual

Page 229

CHAPTER 9 RESET FUNCTION

229

User’s Manual U10676EJ3V0UM

When RESET Signal Asserted

in Standby Mode

When RESET Signal Asserted

During Operation

Hardware

Basic inter-

val timer/

w a t c h d o g

timer

Timer

counter (T0)

Timer

counter (T1)

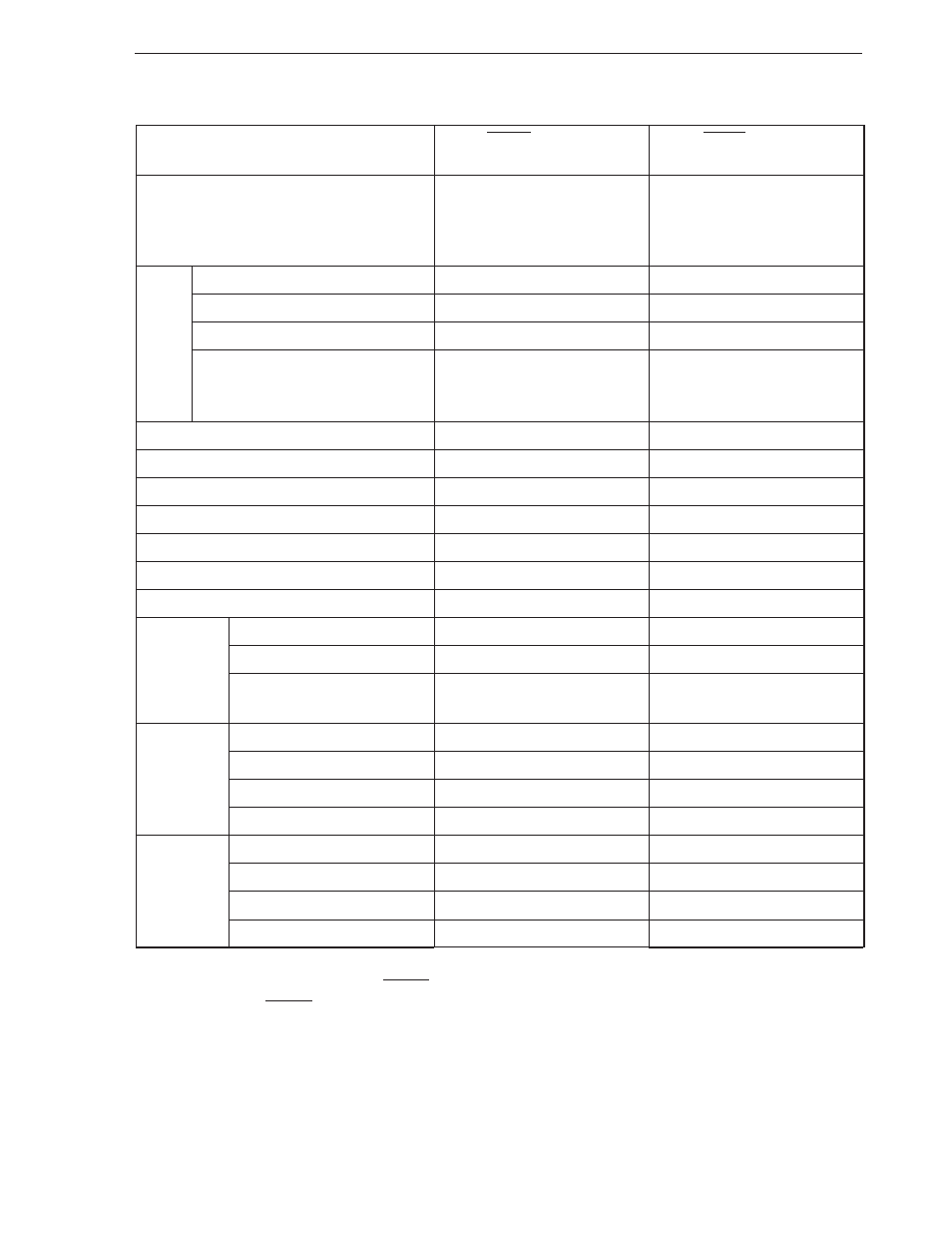

Table 9-1. Status of Each Hardware Unit After Reset (1/3)

Notes

1. If STOP mode is entered during an EEPROM write operation or if HALT mode is entered during a write

operation and then the RESET signal is input, this becomes undefined.

2. If the RESET signal is input during an EEPROM write operation, the address data becomes undefined.

Program counter (PC)

PSW

Carry flag (CY)

Skip flags (SK0-SK2)

Interrupt status flags (IST0, IST1)

Bank enable flags (MBE, RBE)

Stack pointer (SP)

Stack bank select register (SBS)

Data memory (RAM)

Data memory (EEPROM)

EEPROM write control register (EWC)

General-purpose registers (X, A, H, L, D, E, B, C)

Bank select registers (MBS, RBS)

Counter (BT)

Mode register (BTM)

Watchdog timer enable flag

(WDTM)

Counter (T0)

Modulo register (TMOD0)

Mode register (TM0)

TOE0, TOUT F/F

Counter (T1)

Modulo register (TMOD1)

Mode register (TM1)

TOE1, TOUT F/F

Sets lower 4 bits of program

memory address 0000H to

PC11-PC8, and contents of

address 0001H to PC7-PC0

Retained

0

0

Sets bit 6 of program memory

address 0000H to RBE and bit

7 to MBE

Undefined

1000B

Retained

Retained

Note 1

0

Retained

0, 0

Undefined

0

0

0

FFH

0

0, 0

0

FFH

0

0, 0

Same as left

Undefined

0

0

Same as left

Undefined

1000B

Undefined

Retained

Note 2

0

Undefined

0, 0

Undefined

0

0

0

FFH

0

0, 0

0

FFH

0

0, 0