NEC PD754144 User Manual

Page 125

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

125

User’

s Man

ual U10676EJ3V0UM

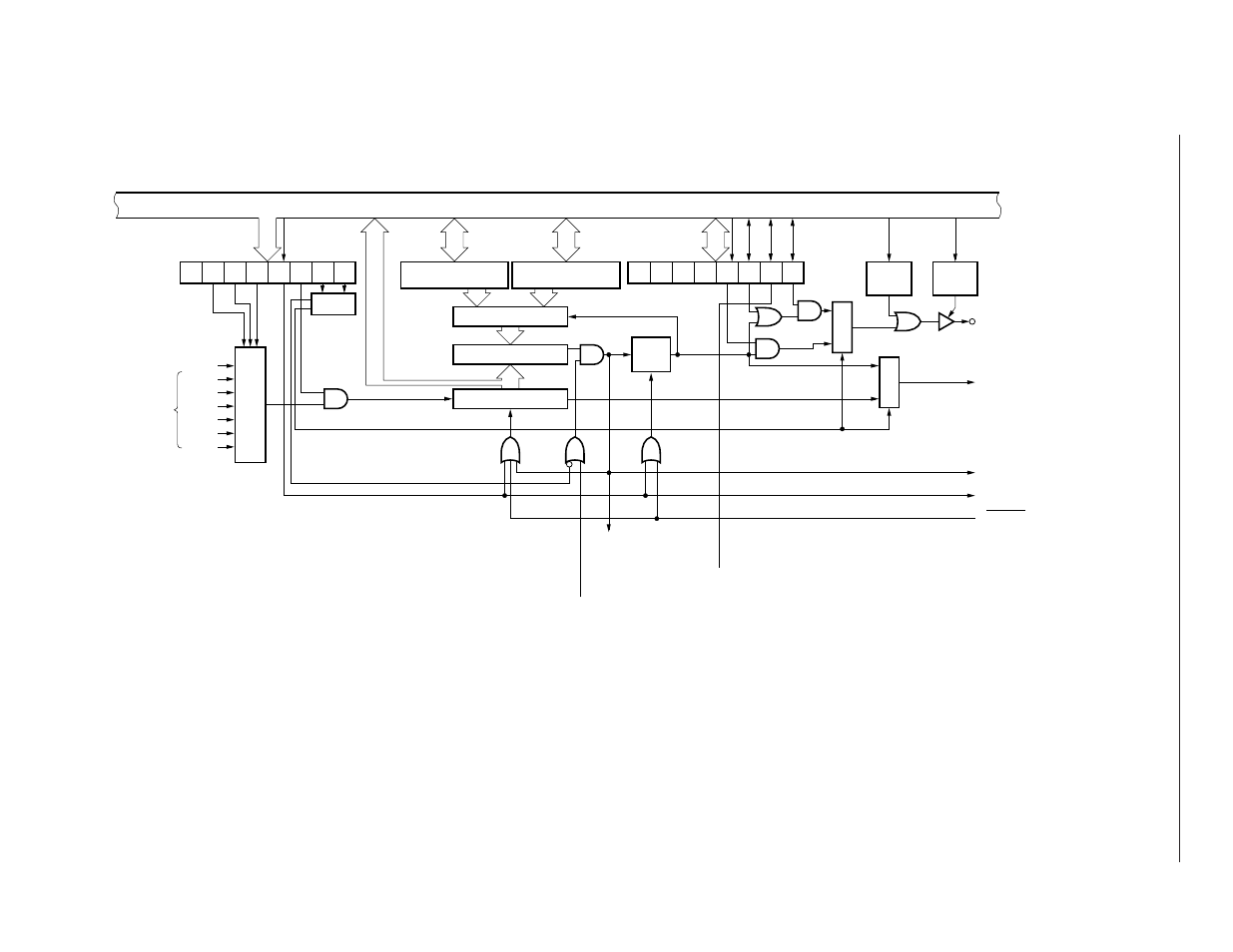

Figure 6-25. Block Diagram of Timer Counter (Channel 2)

Note Execution of the instruction

Caution Be sure to clear bit 7 to 0 when setting data to TC2.

8

Internal bus

–

TM26 TM25 TM24 TM23 TM22 TM21 TM20

From clock

generator

MPX

Decoder

8

High-level period setting

modulo register (8)

8

8

Modulo register (8)

8

MPX (8)

8

Comparator (8)

Count register (8)

8

TOUT

F/F

Clear

IRQT2 c]ear signal

INTT2 (lRQT2 set signal)

TMOD2H

TMOD2

RESET

8

0

–

–

–

TOE2 REMC NRZB NRZ

TC2

Selector

Selector

P32

output

latch

PORT3.2

Port 3

l/O mode

P32/PTO2

Timer counter

(channel 1) clock input

Bit 2 of PMGA

16-bit timer counter mode

Timer operation starts

Timer counter (channel 1)

match signal (in 16-bit timer counter mode)

Timer counter

(channel 1) clear signal

(in 16-bit timer

counter mode)

Timer counter (channel 1)

match signal (in carrier generator mode)

Match

Reset

Re-

load

Overflow

Carrier generator mode

Output buffer

TM2

CP

f

X

/2

f

X

/2

4

f

X

/2

6

f

X

/2

8

f

X

/2

10

SET1

Note

f

X

f

X