2 bit manipulation instruction, 3 string-effect instruction – NEC PD754144 User Manual

Page 235

CHAPTER 11 INSTRUCTION SET

235

User’s Manual U10676EJ3V0UM

11.1.2 Bit manipulation instruction

The

µPD754244 has reinforced bit test, bit transfer, and bit Boolean (AND, OR, and XOR) instructions, in addition

to the ordinary bit manipulation (set and clear) instructions.

The bit to be manipulated is specified in the bit manipulation addressing mode. Three types of bit manipulation

addressing modes can be used. The bits manipulated in each addressing mode are shown in Table 11-1.

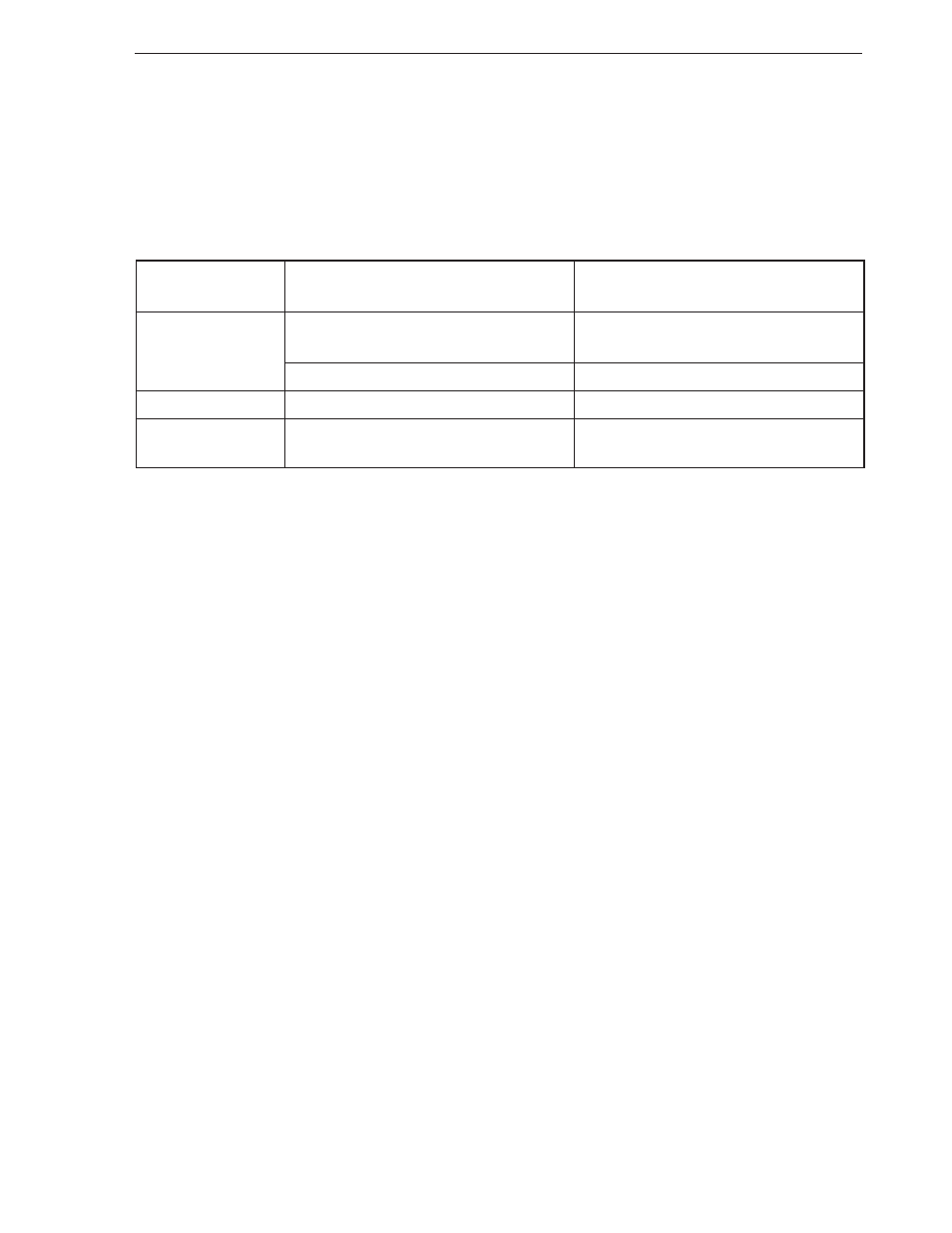

Table 11-1. Types of Bit Manipulation Addressing Modes and Specification Range

fmem. bit

RBE, MBE, IST1, IST0,

FB0H to FBFH

IE

×××, IRQ×××

PORT3, 6, 7, 8

FF0H to FFFH

pmem. @L

BSB0-3, PORT8

FC0H to FFFH

@H+mem. bit

All peripheral hardware units that can be

manipulated bitwise

Remarks

1.

×××: 0, 2, T0, T1, T2, EE

2. MB = MBE

MBS

11.1.3 String-effect instruction

The

µPD754244 has the following two types of string-effect instructions.

(a) MOV A, #n4 or MOV XA, #n8

(b) MOV HL, #n8

“String effect” means locating these two types of instructions at contiguous addresses.

Example A0:

MOV A, #0

A1:

MOV A, #1

XA7:

MOV XA, #07

When string-effect instructions are arranged as shown in this example, and if the address executed first is A0, the

two instructions following this address are replaced with NOP instructions. If the address executed first is A1, the

following instruction is replaced with a NOP instruction. In other words, only the instruction that is executed first is

valid, and all the string-effect instructions that follow are processed as NOP instructions.

By using these string-effect instructions, constants can be efficiently set to the accumulator (register A or register

pair XA) and data pointer (register pair HL).

Addressing Range of Bit That Can be

Manipulated

Peripheral Hardware That Can Be

Manipulated

Addressing

All bits of memory bank specified by MB that

can be manipulated bitwise

.