NEC PD754144 User Manual

Page 194

CHAPTER 7 INTERRUPT AND TEST FUNCTIONS

194

User’s Manual U10676EJ3V0UM

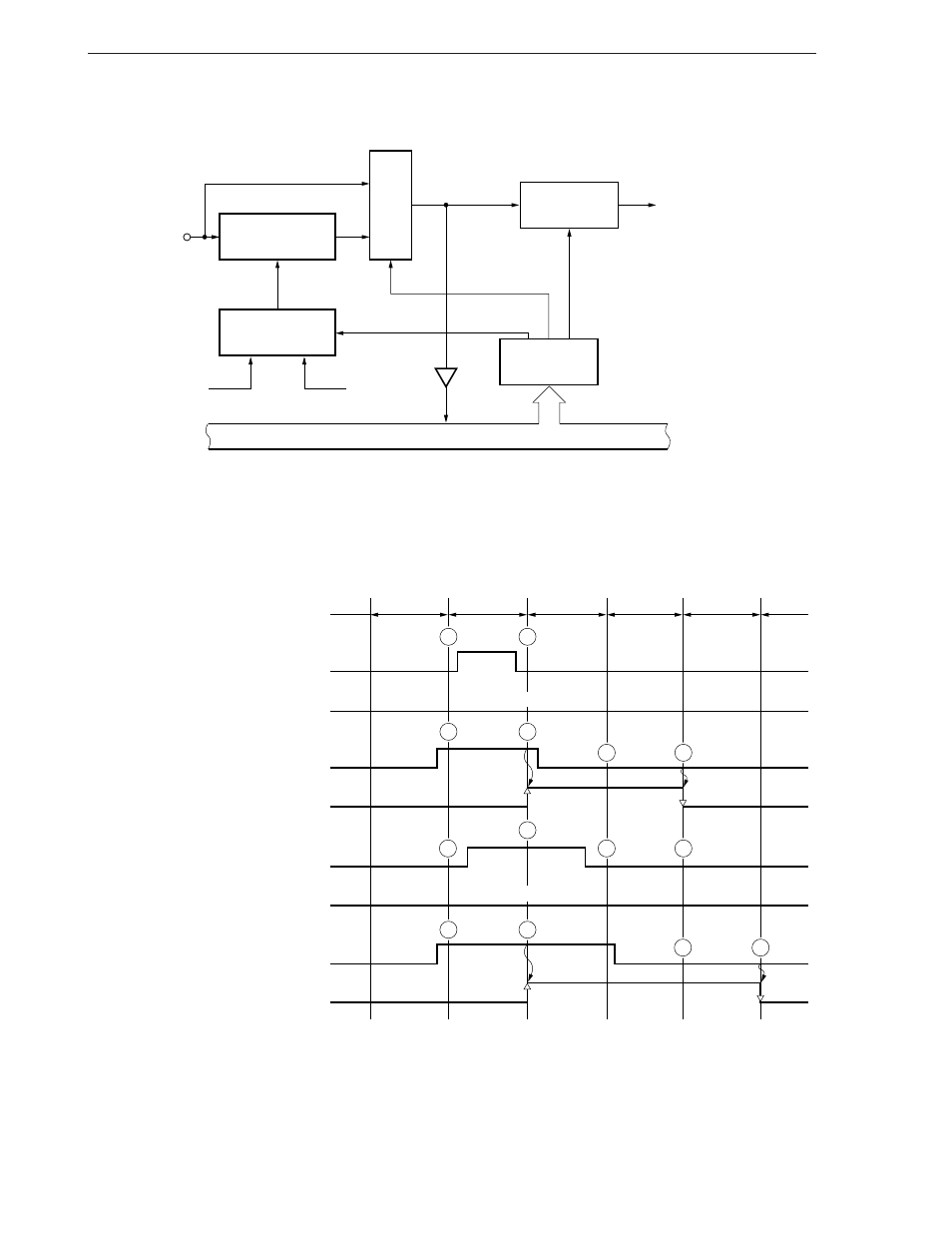

Figure 7-4. Configuration of INT0

Internal bus

4

IM0

Noise eliminator

INT0/P61

Selector

Selector

Φ

f

X

/64

IM03

Edge

detector

INT0

(IRQ0 set signal)

IM00, IM01

IM02

Specifies edge to be detected.

Selects sampling clock.

Input buffer

Note Even if f

X

/64 is selected, the HALT mode cannot be released by INT0.

Figure 7-5. I/O Timing of Noise Eliminator

L

L

H

H

L

L

L

L

H

L

H

H

L

L

Eliminated as noise

Eliminated as noise

t

SMP

t

SMP

t

SMP

t

SMP

t

SMP

<1>

Narrow than sampling cycle

(t

SMP

)

INT0

Shaped output

INT0

Shaped output

INT0

Shaped output

INT0

Shaped output

<2>

1 to 2 times wider than

sampling cycle

(a)

(b)

<3>

More than two times wider

than sampling clock

"L"

"L"

Remark

t

SMP

= t

CY

or 64/f

X

This manual is related to the following products: