NEC PD754144 User Manual

Page 245

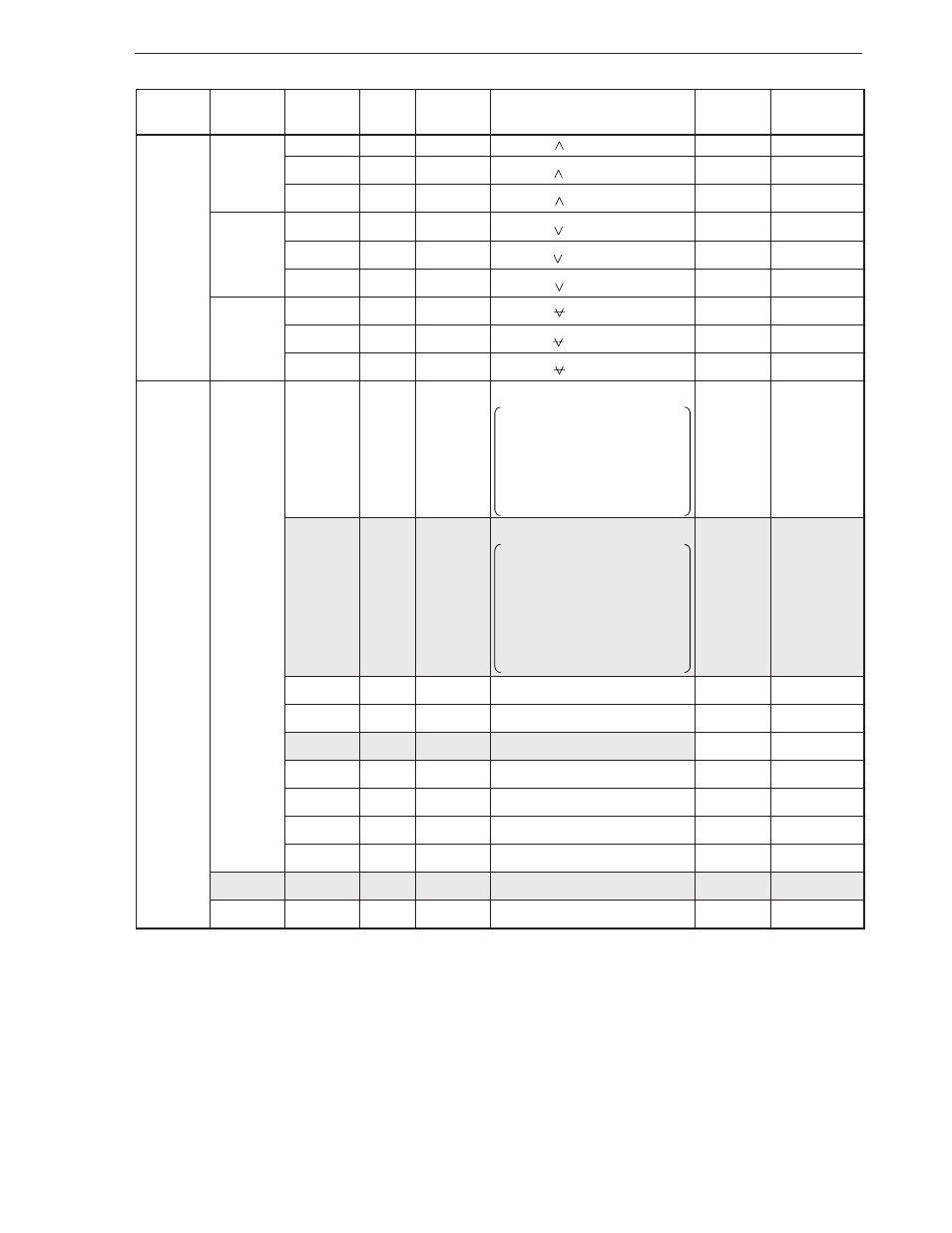

CHAPTER 11 INSTRUCTION SET

245

User’s Manual U10676EJ3V0UM

Machine

Cycle

Instructions

Mnemonic

Operand

Bytes

Operation

Skip Condition

Addressing

Area

AND1

CY, fmem.bit

2

2

CY

← CY (fmem.bit)

*4

CY, pmem.@L

2

2

CY

← CY (pmem

7-2

+ L

3-2

.bit(L

1-0

))

*5

CY, @H + mem.bit

2

2

CY

← CY (H + mem

3-0

.bit)

*1

OR1

CY, fmem.bit

2

2

CY

← CY (fmem.bit)

*4

CY, pmem.@L

2

2

CY

← CY (pmem

7-2

+ L

3-2

.bit(L

1-0

))

*5

CY, @H + mem.bit

2

2

CY

← CY (H + mem

3-0

.bit)

*1

XOR1

CY, fmem.bit

2

2

CY

← CY (fmem.bit)

*4

CY, pmem.@L

2

2

CY

← CY (pmem

7-2

+ L

3-2

.bit(L

1-0

))

*5

CY, @H + mem.bit

2

2

CY

← CY (H + mem

3-0

.bit)

*1

Branch

BR

Note1

addr

–

–

PC

11-0

← addr

*6

Optimum instruction is selected

by assembler from following:

BR !addr

BRCB !caddr

BR $addr1

addr1

–

–

PC

11-0

← addr1

*11

Optimum instruction is selected

by assembler from following:

BR !addr

BRA !addr1

BRCB !caddr

BR $addr1

!addr

3

3

PC

11-0

← addr

*6

$addr

1

2

PC

11-0

← addr

*7

$addr1

1

2

PC

11-0

← addr1

*7

PCDE

2

3

PC

11-0

← PC

11-8

+ DE

PCXA

2

3

PC

11-0

← PC

11-8

+ XA

BCDE

2

3

PC

11-0

← BCDE

Note2

*6

BCXA

2

3

PC

11-0

← BCXA

Note2

*6

BRA

Note1

!addr1

3

3

PC

11-0

← addr1

*11

BRCB

!caddr

2

2

PC

11-0

← caddr

11-0

*8

Notes

1. The shaded portion is supported only in the MkII mode. All others are supported only in the MkI mode.

2. Set 0 to the B register

Memory bit

manipula-

tion