NEC PD754144 User Manual

Page 223

CHAPTER 8 STANDBY FUNCTION

223

User’s Manual U10676EJ3V0UM

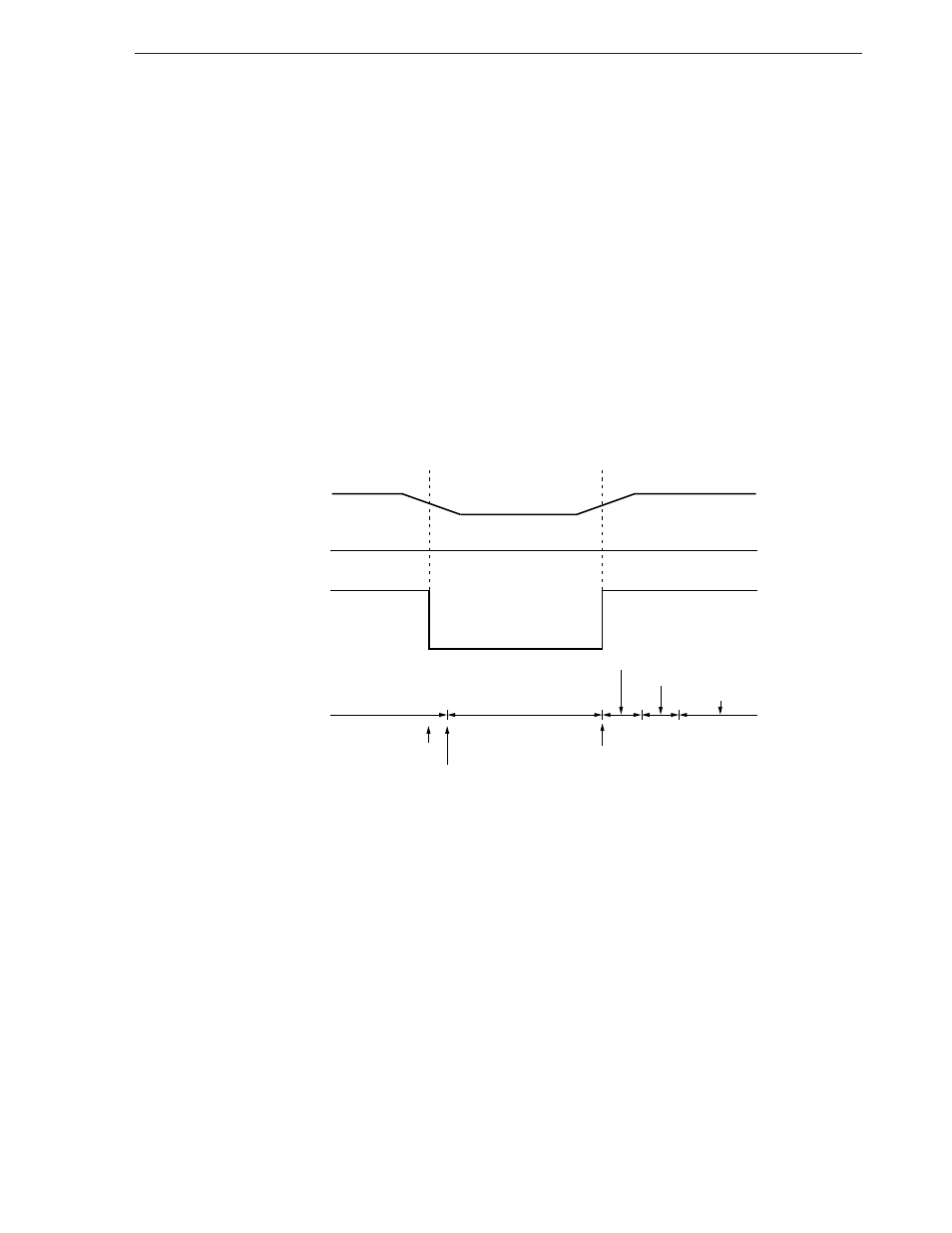

(1) Application example of STOP mode (when using the

µPD754244 at f

X

= 6.0 MHz)

• The STOP mode is set at the falling edge of INT0 and released at the rising edge.

• All the I/O ports go into a high-impedance state (if the pins are externally processed so that the current

consumption is reduced in a high-impedance state).

• Interrupts INTBT and INTT0 are used in the program. However, these interrupts are not used to release the

STOP mode.

• The interrupts are enabled even after the STOP mode has been released.

• After the STOP mode has been released, operation is started with the slowest CPU clock.

• The wait time that elapses after the mode has been released is about 21.8 ms.

• A wait time of 21.8 ms elapses until the power supply stabilizes after the mode has been released. The P61/

INT0 pin is checked twice to prevent chattering.

0 V

V

DD

P61/INT0

CPU operation

STOP instruction

INT0

INT0

About

21.8 ms

Operation mode

STOP mode

HALT mode (wait)

Low-speed operation

High-speed operation

V

DD

pin voltage

About

21.8 ms