Chapter 3 features of architecture and memory map, 1 bank configuration of data memory – NEC PD754144 User Manual

Page 32

32

User’s Manual U10676EJ3V0UM

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP

The 75XL architecture employed for the

µPD754244 has the following features.

•

Internal RAM: 4K words

× 4 bits MAX. (12-bit address)

•

Expandability peripheral hardware

To realize these superb features, the following techniques have been employed.

(1) Bank configuration of data memory

(2) Bank configuration of general-purpose registers

(3) Memory mapped I/O

This chapter describes these features.

3.1 Bank Configuration of Data Memory and Addressing Modes

3.1.1 Bank configuration of data memory

The

µPD754244 is provided with a static RAM at the addresses 000H to 07FH of memory bank 0 of the data memory

space. EEPROM (16

× 8 bits) is allocated to addresses 400H to 41FH of memory bank 4, and peripheral hardware

units (such as I/O ports and timers) are allocated to addresses F80H to FFFH of memory bank 15.

The

µPD754244 employs a memory bank configuration that directly or indirectly specifies the lower 8 bits of an

address by an instruction and the higher 4 bits of the address by a memory bank, to address the data memory space

of 12-bit address (4K words

× 4 bits).

To specify a memory bank (MB), the following hardware units are provided.

•

Memory bank enable flag (MBE)

•

Memory bank select register (MBS)

MBS is a register that selects a memory bank. Memory banks 0, 4, and 15 can be set. MBE is a flag that enables

or disables the memory bank selected by MBS. When MBE is 0, the specified memory bank (MB) is fixed, regardless

of MBS, as shown in Figure 3-1. When MBE is 1, however, a memory bank is selected according to the setting of

MBS, so that the data memory space can be expanded.

To address the data memory space, MBE is usually set to 1 and the data memory of the memory bank specified

by MBS is manipulated. By selecting the mode of MBE = 0 or the mode of MBE = 1 for each processing of the program,

programming can be efficiently carried out.

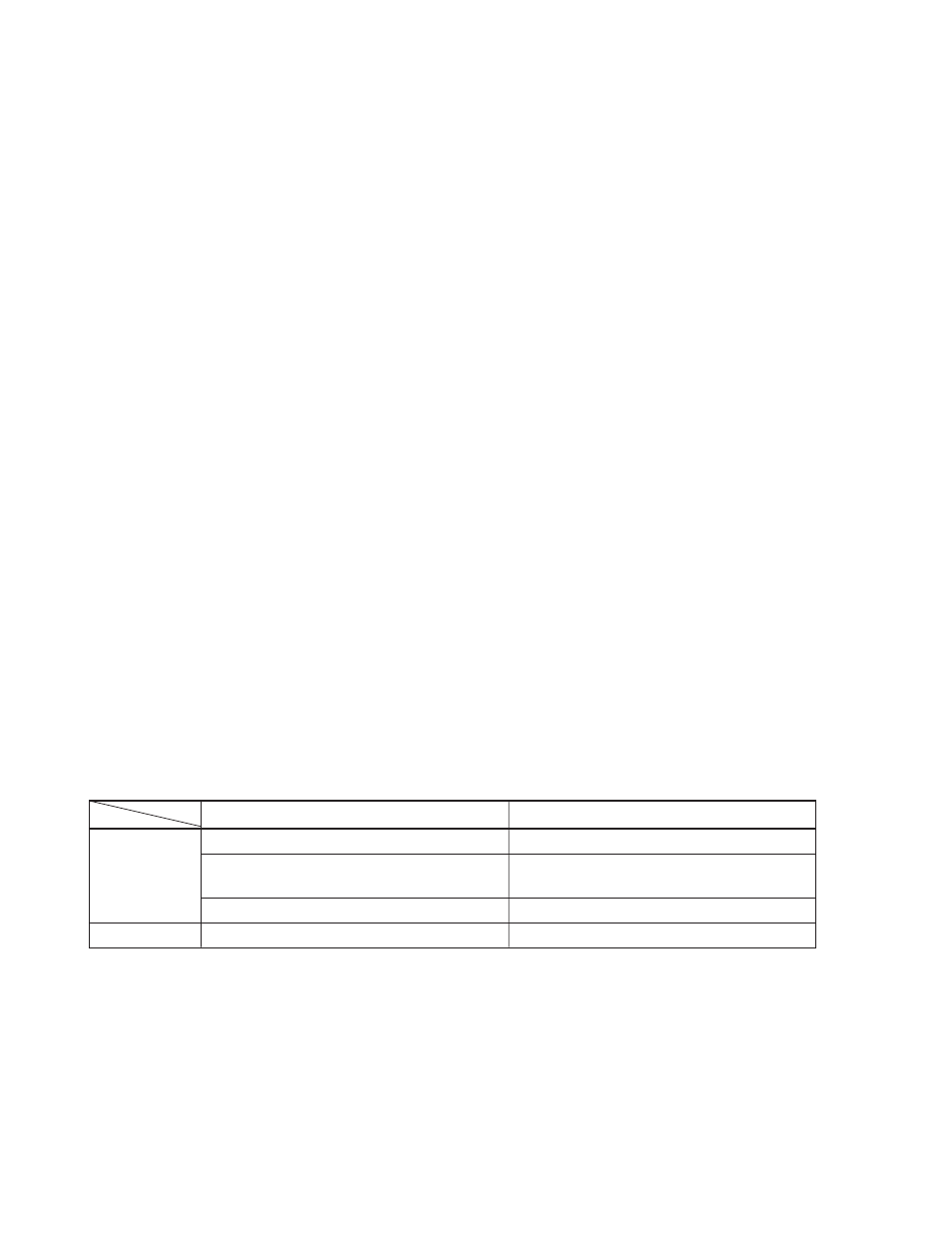

Adapted Program Processing

Effect

MBE = 0 mode

• Interrupt servicing

Saving/restoring MBS unnecessary

• Processing repeating internal hardware

Changing MBS unnecessary

manipulation and stack RAM manipulation

• Subroutine processing

Saving/restoring MBS unnecessary

MBE = 1 mode

• Normal program processing