NEC PD754144 User Manual

Page 230

CHAPTER 9 RESET FUNCTION

230

User’s Manual U10676EJ3V0UM

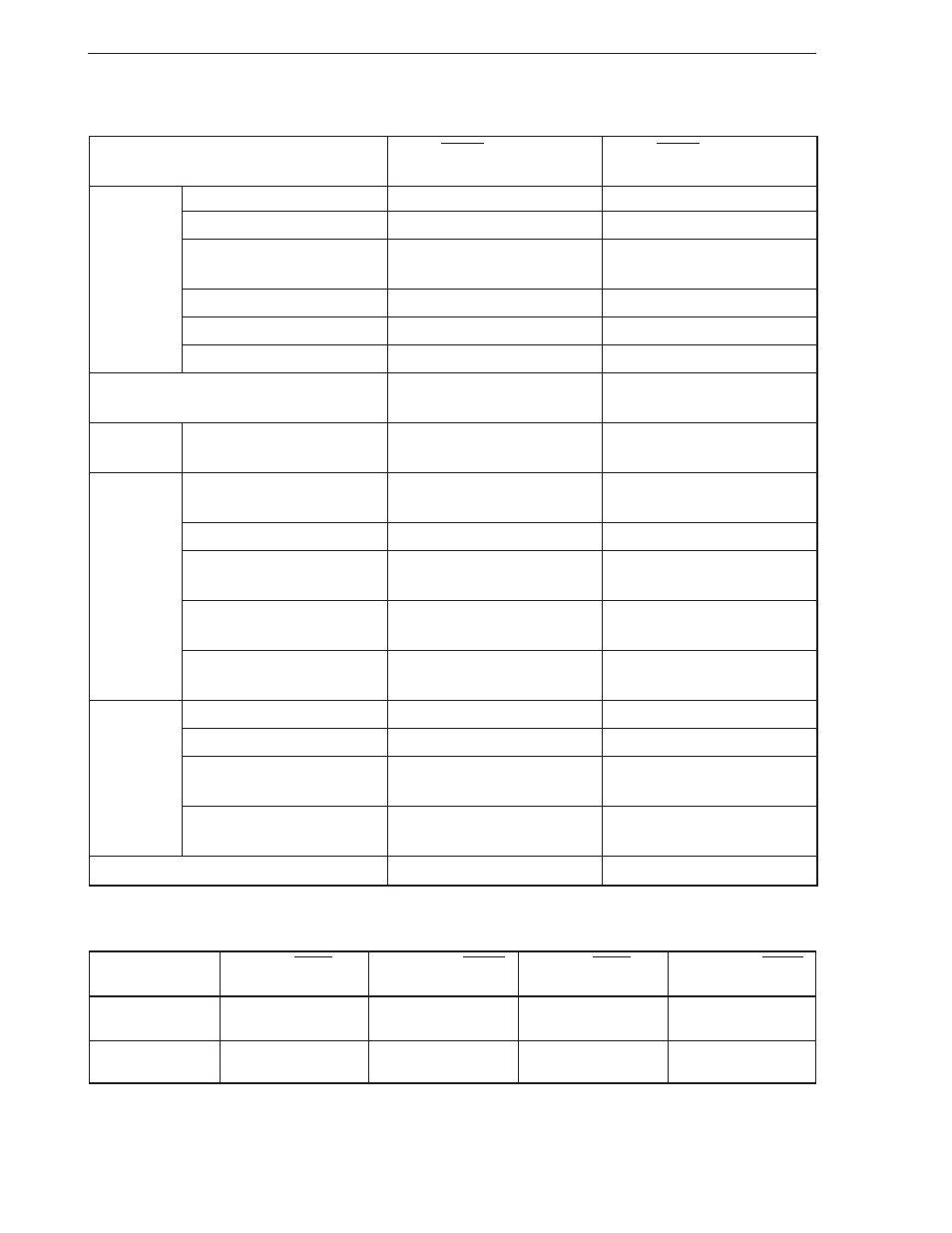

Counter (T2)

Modulo register (TMOD2)

High-level period setting

modulo register (TMOD2H)

Mode register (TM2)

TOE2, TOUT F/F

REMC, NRZ, NRZB

Programmable threshold port mode register

(PTHM)

Processor clock control

register (PCC)

Interrupt request flag

(IRQ

×××)

Interrupt enable flag (IE

×××)

Interrupt master enable flag

(IME)

Interrupt priority select

register (IPS)

INT0, 2 mode registers

(IM0, IM2)

Output buffer

Output latch

I/O mode registers

(PMGA, PMGC)

Pull-up resistor specification

register (POGA, POGB)

Table 9-1. Status of Each Hardware Unit After Reset (2/3)

When RESET Signal Asserted

in Standby Mode

When RESET Signal Asserted

During Operation

Hardware

0

FFH

FFH

0

0, 0

0, 0, 0

00H

0

Reset (0)

0

0

0

0, 0, 0

Off

Cleared (0)

0

0

0

FFH

FFH

0

0, 0

0, 0, 0

00H

0

Reset (0)

0

0

0

0, 0, 0

Off

Cleared (0)

0

0

Timer

counter (T2)

Interrupt

function

Clock generation

circuit

Digital ports

Bit sequential buffers (BSB0 to BSB3)

Retained

Undefined

Table 9-1. Hardware Status After Reset (3/3)

Hardware

Generation of RESET Signal

Generation of RESET

Generation of RESET Signal

Generation of RESET

by Key Return Reset

Signal in Standby Mode

by WDT in Operation

Signal in Operation

Watchdog flag

Retains the previous

0

1

0

(WDF)

state.

Key return flag

1

0

Retains the previous

0

(KRF)

state.