NEC PD754144 User Manual

Page 123

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

123

User’

s Man

ual U10676EJ3V0UM

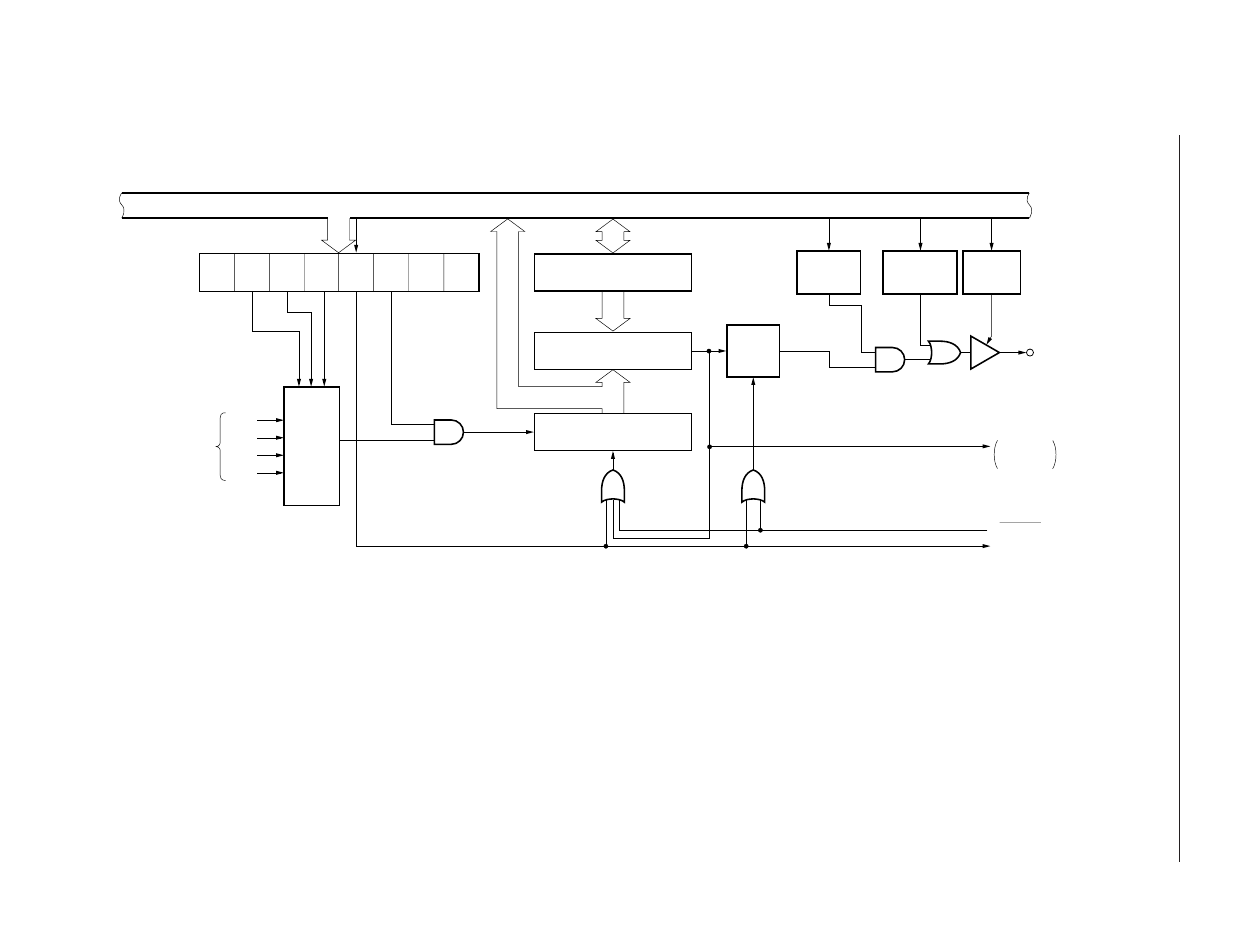

Figure 6-23. Block Diagram of Timer Counter (Channel 0)

Note Execution of the instruction

Caution Be sure to clear bits 1 and 0 to 0 when setting data to TM0.

–

TM06 TM05 TM04 TM03 TM02

0

0

TM0

8

Internal bus

8

8

Modulo register (8)

MPX

From clock

generator

SET1

Note

TMOD0

8

Comparator (8)

8

Count register (8)

T0

CP

Clear

Timer operation starts

TOUT

F/F

Reset

Co-

inci-

dence

T0 enable

flag

TOE0

P30

output latch

PORT3.0

Port 3

I/O mode

Bit 0 of PMGA

P30/PTO0

Output buffer

INTT0

lRQT0

set signal

IRQT0 c]ear

signal

RESET

f

X

/2

4

f

X

/2

6

f

X

/2

8

f

X

/2

10

This manual is related to the following products: