NEC PD754144 User Manual

Page 104

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

104

User’s Manual U10676EJ3V0UM

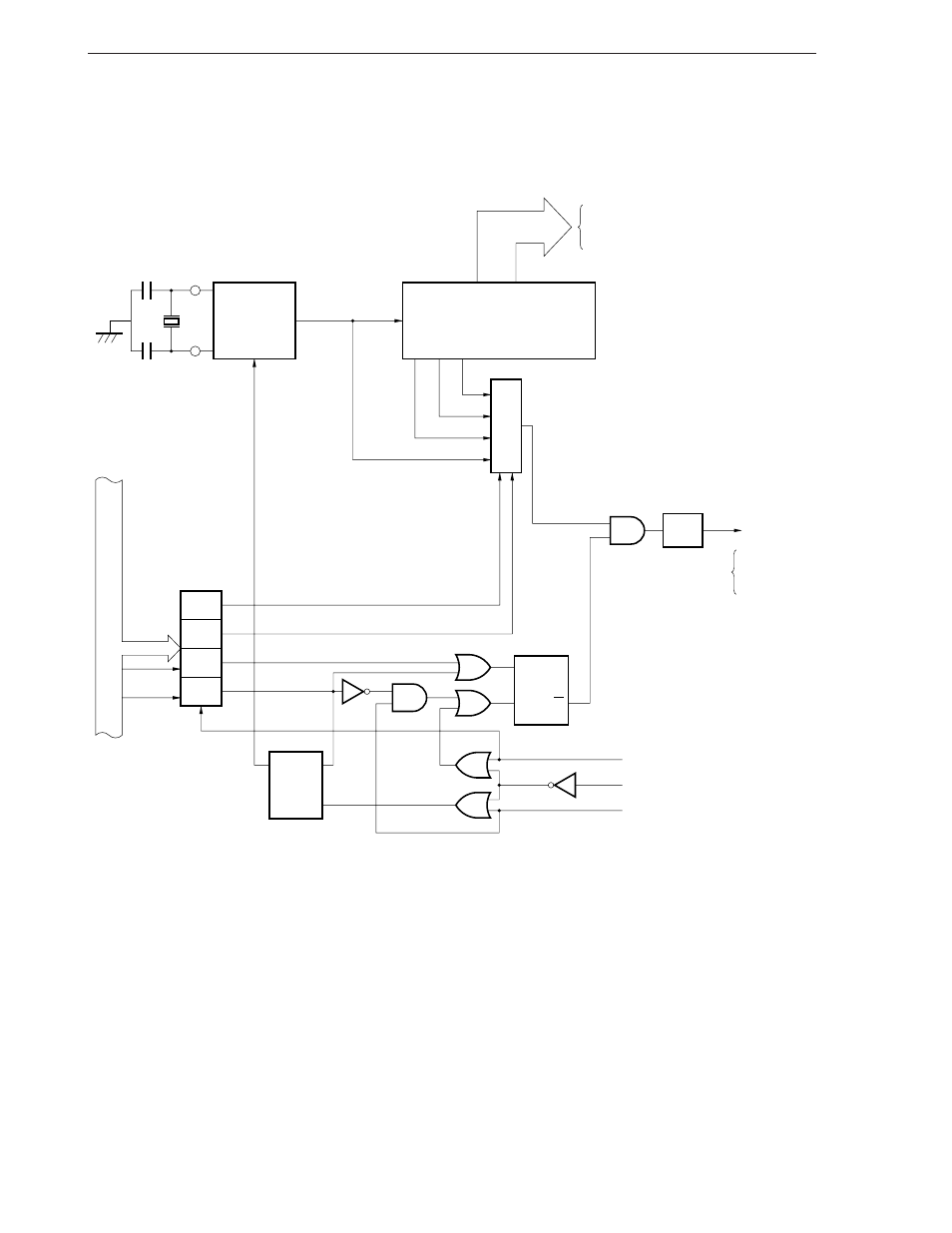

Figure 6-14. Block Diagram of Clock Generator (2/2)

(b)

µPD754244 Crystal/Ceramic Oscillation

X1

X2

System

clock

oscillator

Oscillation stops

1/2 1/4 1/16

f

X

Divider

1/4

Φ

HALT F/F

S

R

Q

S

R

Q

STOP F/F

PCC0

PCC1

PCC2

PCC3

PCC2,

PCC3

clear

HALT

Note

STOP

Note

Wait release signal from BT

PCC

4

· Basic interval timer (BT)

· Timer counter

· INT0 noise eliminator

1/1 to 1/4096

· CPU

· INT0 noise

eliminator

Divider

Selector

Internal bus

Reset signal

(selectable by mask option)

Standby release signal from

interrupt controller

Note

Instruction execution

Remarks 1.

f

X

: System clock frequency

2.

Φ = CPU clock

3.

PCC: Processor Clock Control Register

4.

One clock cycle (t

CY

) of the CPU clock is equal to one machine cycle of the instruction.