10 pld boot bank register, Table 5-12, Pld boot bank register – Artesyn MVME2500 ECC Installation and Use (August 2014) User Manual

Page 95: Chapter 5, pld boot bank register, on

Memory Maps and Registers

MVME2500-ECC Installation and Use (6806800N30F)

95

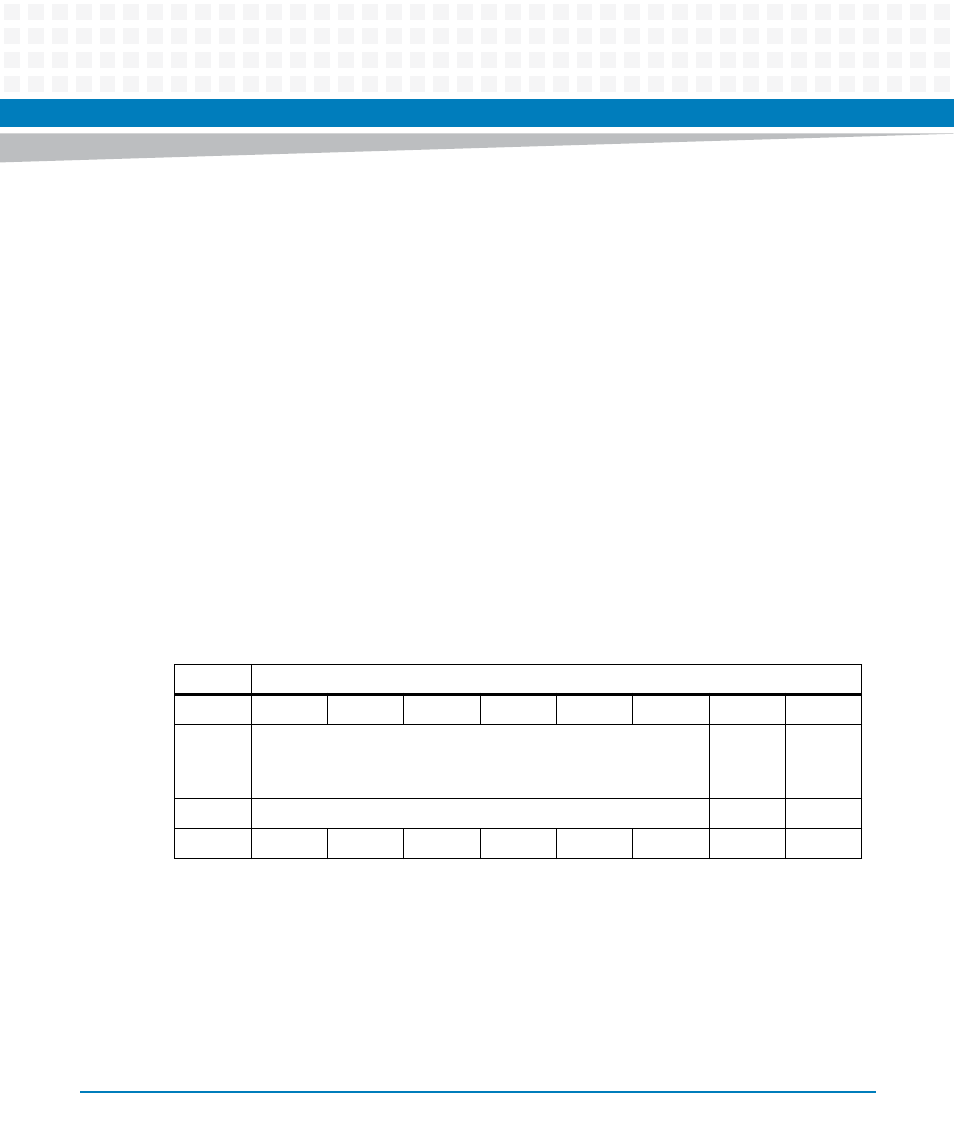

5.4.10 PLD Boot Bank Register

The MVME2500-ECC PLD provides an 8-bit register which is used to declare successful U-Boot

loading, indicating the SPI boot bank priority and actual SPI bank it booted from.

Field Description

BDFAIL_N

TSI148 BDFAIL_N Pin out

1 - No TSI Fail

0 - TSI Fail

NORMAL_ENV

Normal Environment Switch Indicator

1 - Use safe ENV

0 - Use normal ENV

SCON

System Controller Indicator

1 - System Controller

0 - Non-system Controller

Table 5-12 PLD Boot Bank Register

REG

PLD Boot Bank - 0xFFDF0050

Bit

7

6

5

4

3

2

1

0

Field

SPI_GOODReg

(write 0xA4 into this reg to indicate successful loading of the U-

Boot.

BOOT_B

LOCK_A

BOOT_S

PI

OPER

R/W

R

R

RESET

0

0

0

0

0

0

X

0