5 external timer registers, 1 prescaler register, Table 5-21 – Artesyn MVME2500 ECC Installation and Use (August 2014) User Manual

Page 104: Prescaler register

Memory Maps and Registers

MVME2500-ECC Installation and Use (6806800N30F)

104

5.5

External Timer Registers

The MVME2500-ECC provides a set of tick timer registers to access the three external timers

implemented in the timers/registers PLD. These registers are 32-bit and are word writable. The

following sections describe the timer prescaler and control registers.

5.5.1

Prescaler Register

The prescaler adjust value is determined by this formula:

Prescaler Adjust = 256-(CLKIN/CLKOUT)

CLKIN is the input clock source in MHz, and CLKOUT is the desired output clock reference in

MHz.

The prescaler provides the clock required by each of the three times. The tick timers require a

1 MHz clock input. The input clock to the prescaler is 25 MHz. The default value is set for

0x00E7, which gives a 1 MHz reference clock for a 25 MHz input clock source.

Field Description

Count

Count. These bits define the watchdog timer count value. When the

watchdog counter is enabled, it will count up from zero (reset value) with a 1

ms resolution until it reaches the COUNT value set by this register. Watchdog

will generate a soft reset signal if it bites.

Setting this register to 0xEA60 or 60,000 counts will provide a watchdog

timeout of 60 seconds.

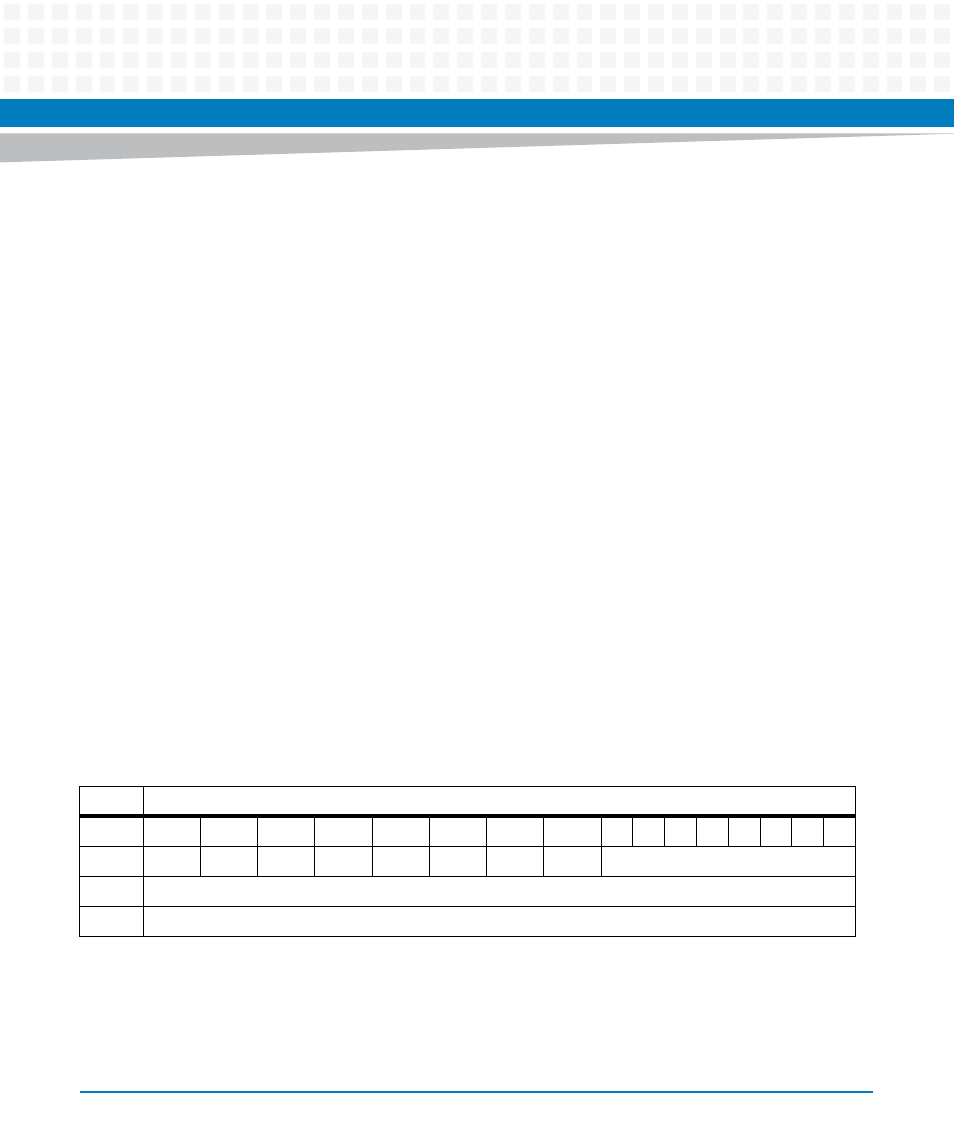

Table 5-21 Prescaler Register

REG

Prescaler Register - 0xFFC80100

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

Prescaler Register (8-bits)

OPER

R/W

RESET

0x00e7