14 pld gpio2 interrupt register, Table 5-16, Pld gpio2 interrupt register – Artesyn MVME2500 ECC Installation and Use (August 2014) User Manual

Page 100

Memory Maps and Registers

MVME2500-ECC Installation and Use (6806800N30F)

100

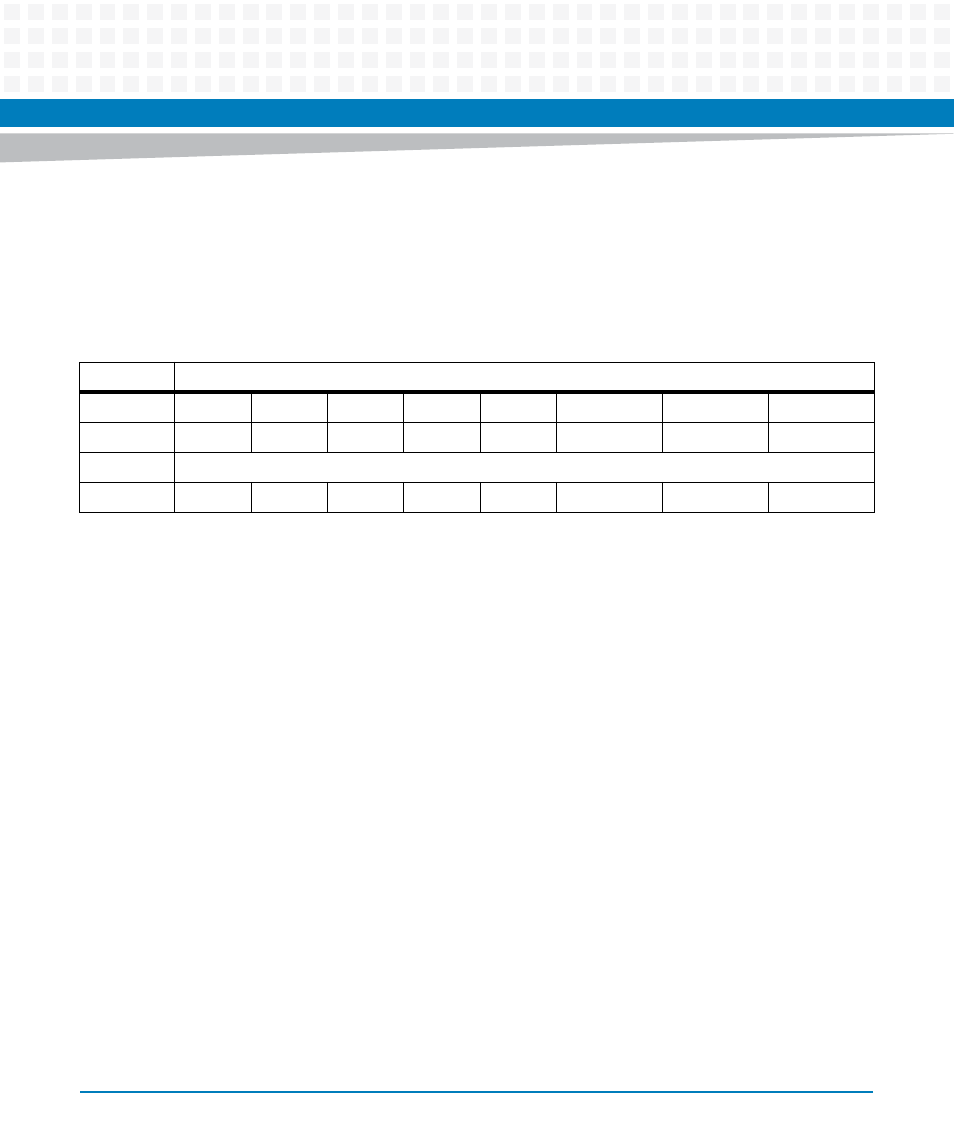

5.4.14 PLD GPIO2 Interrupt Register

The Abort switch, Tick Timer 0, 1 and 2 interrupts are ORed together. The MVME2500-ECC

provides an interrupt register that the system software reads to determine which device the

interrupt originated from. GPIO2 will be driven "low" if any of the interrupts asserts.

Table 5-16 PLD GPIO2 Interrupt Register

REG

PLD Write Protect I2C Debug- 0xFFDF0095

Bit

7

6

5

4

3

2

1

0

Field

RSVD

RSVD

RSVD

RSVD

NMI

TICK0_INT

TICK1_INT

TICK2_INT

OPER

R

RESET

0

0

0

0

0

0

0

0

Field Description

NMI

Abort switch interrupt if pressed less than three seconds.

1 - Interrupt enabled

0 - No Interrupt

TICK0_INT

Tick Timer 0 interrupt

1 - Interrupt enabled

0 - No Interrupt

TICK1_INT

Tick Timer 1 interrupt

1 - Interrupt enabled

0 - No Interrupt

TICK2_INT

Tick Timer 2 interrupt

1 - Interrupt enabled

0 - No Interrupt