7 clock distribution, Table 7-6, Clock distribution – Artesyn MVME2500 ECC Installation and Use (August 2014) User Manual

Page 127: Programming model

Programming Model

MVME2500-ECC Installation and Use (6806800N30F)

127

7.7

Clock Distribution

The clock function generates and distributes all of the clocks required for system operation.

The ICS9FG108 is used to generate all the required PCI-E clocks. The 25 MHz clocks for the

Ethernet PHY and SATA bridge are supplied by ICS83905. Most of the QorIQ P2020 clocks are

generated by ICS840S07I chip. Additional clocks required by individual devices are generated

near the devices using individual oscillators. The following table lists the clocks required on the

MVME2500-ECC along with the frequency and source.

SETA

External address termination

0 - Access is terminated internally by the memory controller unless the

external device asserts LGTA earlier to terminate the access.

TRLX Timing

Relaxed

0 - Normal timing is generated by the GPCM.

EHTR

Extended hold time on read accesses.

0 - The memory controller generates normal timing. No additional cycles

are inserted

EAD

External address latch delay

0 - No additional bus clock cycles (LALE asserted for one bus clock cycle

only)

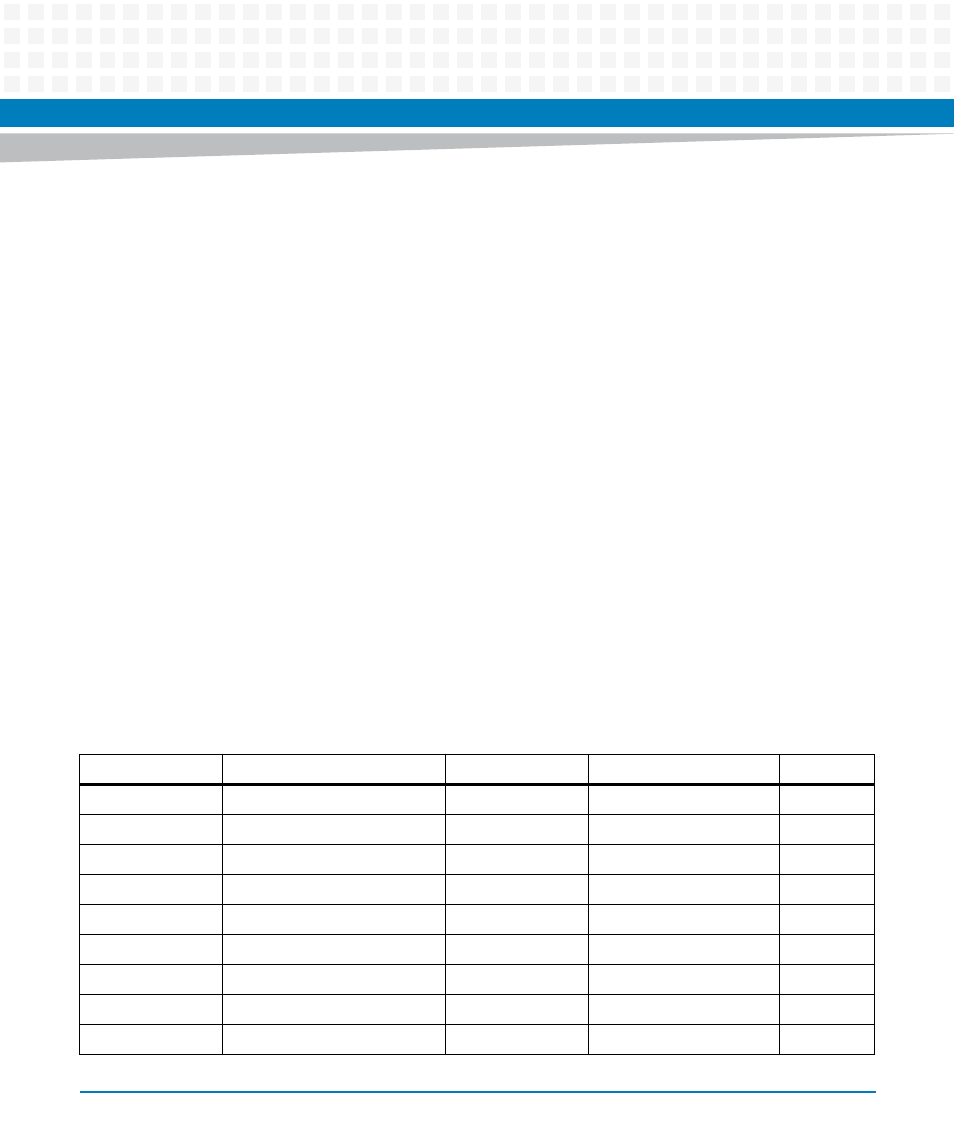

Table 7-6 Clock Distribution

Device

Clock Signal

Frequency

Clock Tree Source

VIO

QorIQ P20x0

CPU_SYSCLK

100MHz

ICS840S07I

+3.3V

QorIQ P20x0

CPU_DDR_CLK

100MHz

ICS840S07I

+3.3V

QorIQ P20x0

CLK_PCI_BR3

133Mhz

ICS840S07I

+3.3V

QorIQ P20x0

EC_GTX_CLK125

125Mhz

ICS840S07I

+3.3V

ICS840S07I

CLK_25MHZ_ICS840S07

25Mhz

ICS83905AGILF

+3.3V

88SE6121

CLK_88SE6121_25MHZ

25Mhz

ICS83905AGILF

+3.3V

ICS9FG108

CLK_25MHZ_ICS9FG108

25Mhz

ICS83905AGILF

+3.3V

BCM54616S

BP_PHY_25MHZ_CLK

25Mhz

ICS83905AGILF

+3.3V

BCM54616S

FP_PHY_25MHZ_CLK

25Mhz

ICS83905AGILF

+3.3V