Programming model – Artesyn MVME2500 ECC Installation and Use (August 2014) User Manual

Page 120

Programming Model

MVME2500-ECC Installation and Use (6806800N30F)

120

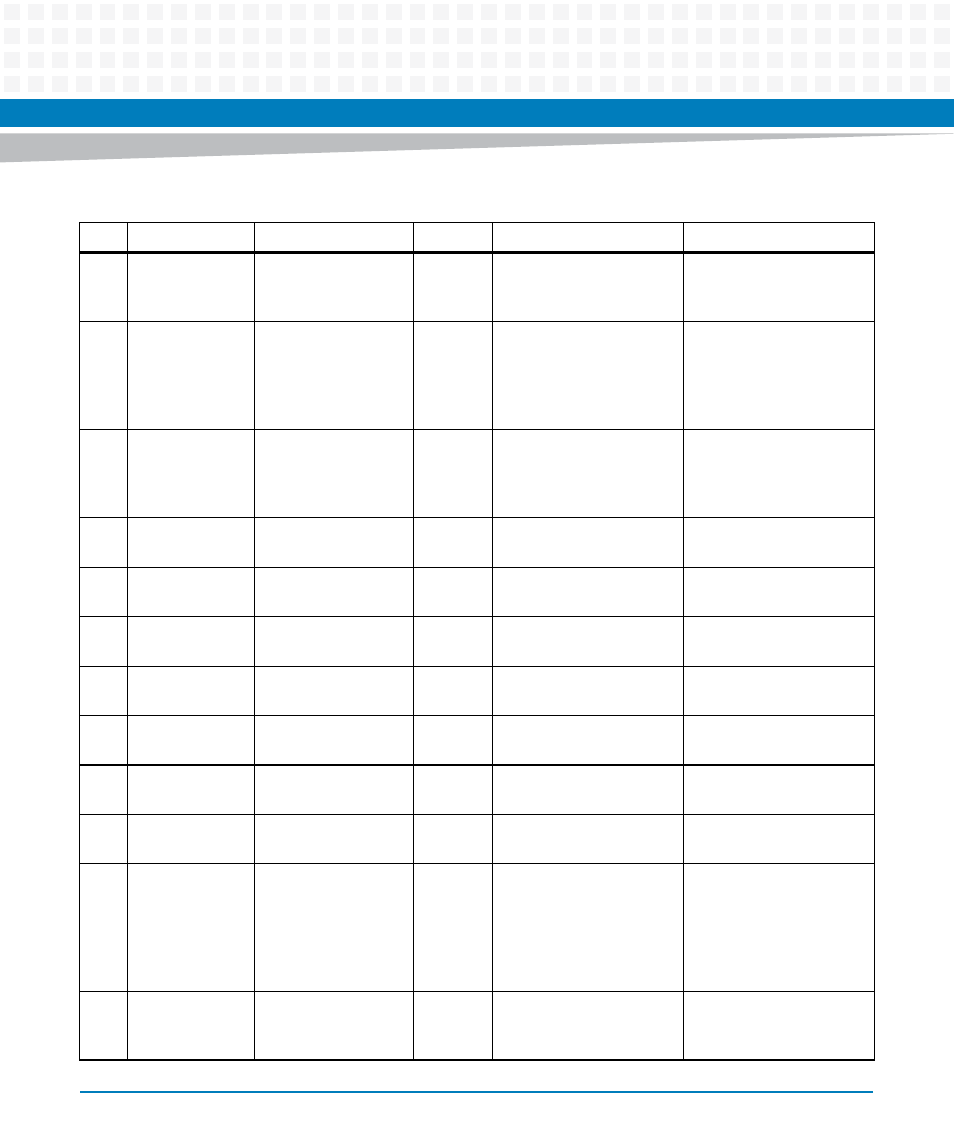

6

Boot Sequence

LGPL3/LFWP, LGPL5

11

CFG_BOOT_SEQ[1:0] =

BOOT SEQUENCE

DISABLED

7

Memory Debug

Config

DMA2_DACK0

1

Debug information from

the DDR SDRAM

controller is driven on the

MSPCID and MDVAL signs

(default)

8

DDR Debug

Config

DMA2_DDONE0

1

Debug information is not

driven on ECC pins. ECC

function in their normal

mode (default).

9

ELBCECC Enable

Config

MSRCID0

0

Default operation: eLBC

ECC checking is disabled

10

Platform Speed

LA23

1

CFG_PLAT_SPEED:1=CCB

CLOCK > = 333 MHz

11

CORE 0 Speed

LA24

1

CFG_CORE0_SPEED:1=C

ORE FREQ>= 1000 MHz

For 1200 MHz board

configuration

12

0

CFG_CORE0_SPEED:0=C

ORE FREQ<=1000 MHz

For 800 MHz board

configuration

13

CORE 1 Speed

LA26

1

CFG_CORE1_SPEED:1=C

ORE FREQ>=1000 MHz

For 1200 MHz board

configuration

14

0

CFG_CORE1_SPEED:0=C

ORE FREQ<=1000 MHz

For 800 MHz board

configuration

15

DDR Controller

Speed

LA26

1

CFG_DDR_SPEED:1=DDR

FREQ>= 500 MHz

16

Engineering use

LA[22:20]

UART_SOUT[0],

TRIG_OUT,

MSRCID[1],

MSRCID[4],

DMA1_DDONE_B[0]

111111

11

Default (for future use)

17

SerDes Ref

Clock Config

TSEC_1588_ALARM

_OUT1

1

SerDes expects a 100

MHz reference clock

frequency (default).

Table 7-1 POR Configuration Settings (continued)

CONFIG

CONFIG PINS

CONFIG

SELECTION

REMARKS